# LATCH-UP CHARACTERISTICS OF A TRENCH-GATE CONDUCTIVITY MODULATED POWER TRANSISTOR

Cai Jun<sup>1</sup>, Johnny K.O. Sin<sup>1</sup>, Wai Tung Ng<sup>2</sup>, Peter P.T. Lai<sup>3</sup>

<sup>1</sup>Dept. of Electrical and Electronic Engineering Hong Kong University of Science and Technology Clear Water Bay, Hong Kong Tel: (852)2358-7052 Fax: (852)2358-1485

University of Toronto Toronto, Ontario, Canada

<sup>2</sup>Dept. of Electrical and Computer Engineering <sup>3</sup> Dept. of Electrical and Electronic Engineering University of Hong Kong Pokfulam Road, Hong Kong

Abstract - In this paper, a new conductivity modulated power transistor, called the Lateral Trench-Gate Bipolar Transistor (LTGBT), is presented. The current at which the latch-up occurs in the structure is estimated in comparison with that of the LIGBT. The latch-up current density for the LTGBT exhibits more than 7.7 times improvement over the LIGBT. The dependence of the latchup current density on the design of the n+ and p+ cathode regions of the structure is also examined. The maximum controllable latch-up current density is found to increase with decreasing the space between the trench gate and the p+ cathode.

## I. INTRODUCTION

Power transistors to be used in Power Integrated Circuits (PIC) are required to have low on-resistance, fast switching speed, and high breakdown voltage. The LIGBTs [1,2] are promising power devices for high voltage PIC applications due to their low gate drive and low onresistance. In these devices, the high current handing capability relies on conductivity modulation of the high resistivity drift region by injection of minority carriers. However, occurrence of latch-up due to the existance of the parasitic thyristor inherent in the structure must be prevented for safe operation of the device.

In this paper, the LTGBT structure [3] for improving the latch-up characteristics is presented. Numerical on the dynamic latch-up analysis characteristics of the structure will be examined. The dependence of the latch-up current density on the design of the n+ and p+ cathode regions of the structure will also be discussed.

## II. DEVICE STRUCTURE AND OPERATION

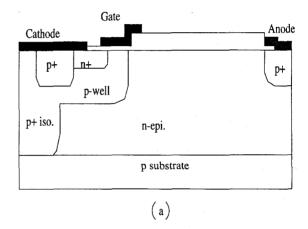

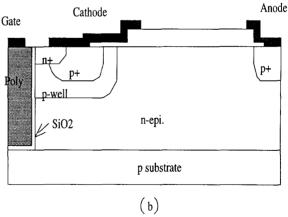

Fig.1 illustrates both the LIGBT and the LTGBT

Fig.1 Schematic cross section of (a) the LIGBT and (b) the LTGBT

structures. The main differences between the LIGBT and the LTGBT are the placement of the MOS gate region and the arrangement of the locations of the n+ and p+ cathode regions. In the LTGBT the MOS gate is formed using a vertical trench with the contact of the p-well region located in front of the n+ cathode. The p-well is connected to the n+ cathode through the p+ cathode. Existing of the p-well between the gate and anode regions facilitates the collection of holes by the p+ cathode contact, so holes will not flow through the area underneath the n+ cathode. At the on-state, the vertical channel depletion region can also divert holes to flow near that region and reduce the number of holes to flow underneath the n+ cathode. All of these allow holes to be collected effectively by the p+ cathode through the p-well before reaching the n+ cathode, and latchup of the structure at high current level can be prevented. Furthermore, the vertical trench gate structure can reduce the unit cell size and increase channel density.

Operation of the LTGBT is identical to that of the LIGBT. In the forward active mode of operation, a positive voltage is applied to the anode relative to the cathode. Anode current starts to flow at gate voltages higher than the threshold voltage and a anode voltage at approximately one diode drop. At a higher anode voltage, the anode pn junction starts to turn on and injects holes into the n epi of the transistor. Some of these holes will recombine with the electrons flowing in from the vertical channel, and some of them will flow from the n epi to the p well and be collected by the p+ cathode without flowing through the area underneath the n+ cathode. So they do not cause latchup. To improve the latch-up characteristics of the structure, it is required to make the n+ cathode region short. However, minimum length of the n+ region is limited by the photolithography capability. For a technology with 2 um alignment tolerance, the minimum n+ length will be about 8 um. This will make the device to latchup at about 700 A/cm2 for the present design. One possible way to further improve the latchup without the need of expensive photolithography is to make use of the differential junction depth for the n+ and p+ cathode regions. With the p+ junction depth deeper than the n+ junction depth and the p+ concentration lower than that of the n+ concentration, the long n+ cathode region needed will be provided at the surface, and its effect on latchup can be eliminated by overlapping with the p+ cathode. In this way, the device will have effectively a very short n+ cathode, depending on the amount of overlaping. Since electrons flowing through the vertical channel, at the on-state, travel a longer distance deep into the bulk before recombination, the holes recombining with the electrons there will also take a long path. So the LTGBT is expected to have a slightly larger on-resistance as compared to the LIGBT.

# III. TWO-DIMENSIONAL SIMULATION

To analyze the latchup performance of the LTGBT, numerical simulations were performed using the two dimensional device simulator MEDICI[4]. MEDICI

allows the characteristics of the on-state and off-state performance of such a complex structure to be simulated. The LTGBT used in the simulation is shown in Fig.1(b) which is designed to have a drift region of 40 um. The thickness of the n epi is 4 um. The p-well has a surface concentration of 1E17 cm-3 and a depth of 2 um. The channel length is 1.5 um.

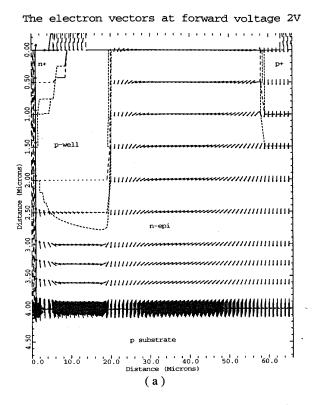

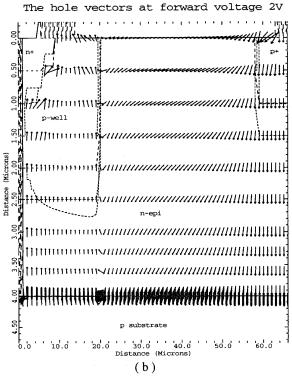

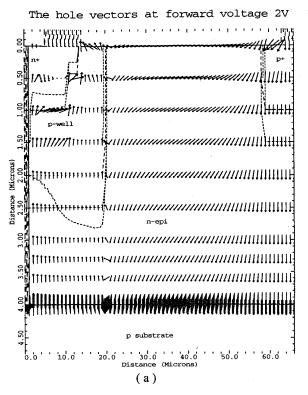

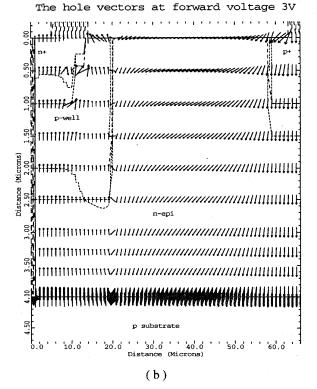

The electron and hole current vectors at the onstate with a n+ cathode length of 7.5 um are shown in Fig.2(a) and 2(b), respectively. It is obversed that the electrons flow from the channel to the n-drift region, and the holes are injected from the p+ anode and flow into the p-well. Also, the area underneath the n+ cathode has a small number of holes. At a longer n+ cathode (12 um, for example), more holes are shown to flow in the area underneath the n+ cathode (Fig. 3(a)) with the same forward voltage of 2 V. At a higher forward voltage, the hole current eventually turns on the p-well / n+ cathode junction, and holes start to flow into the n+ cathode as shown in Fig.3 (b). In this situation, latch-up of the structure occurs.

For a comparision, at a on-state current density of 90 A/cm2 with a gate bias of 20 V, the forward voltage of the LIGBT and LTGBT are 1.7 V and 2.0 V, respectively. The forward voltage for the LTGBT is about 0.3V larger than that of the LIGBT. This is due to the longer path the electrons have to travel and the loss of some holes to the p+cathode without going through recombination. This makes the LTGBT has a current handling capability lower than that of the LIGBT. However, the dynamic latch-up current for the LIGBT and LTGBT at the same n+ cathode length of 5 um are approximately 100A/cm2 and over 770A/cm2, respectively. This latchup current density comparision exhibits a 7.7 times improvement in the LTGBT.

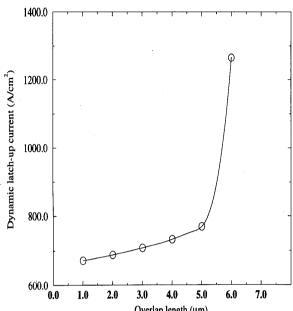

To characterize the latch-up sensitivity of the LTGBT at different p+ cathode depths and at different overlap lengths for the p+ and n+ cathodes diffusions, the dynamic latchup characteristics of the LTGBT were simulated with different values of p+ cathode depth and n+ to p+ overlaps. The simulations were done at a gate voltage of 20 V. At a n+ cathode depth of 0.5 um, the maximum value of the n+ cathode length with no latch-up is 5 um, 7 um, and 9 um for the devices with p+ cathode depth of 0.5 um, 1 um, and 1.5 um, respectively. To verify the ruggedness of the LTGBT at the different overlap lengths, the latchup characteristics of the LTGBT with a p+ cathode depth of 1.5 um and n+ cathode lengh and depth of 10 um and 0.5 um, respectively, were simulated at a gate voltage of 20 V. Fig. 4 shows the latch-up current density as a function of the overlap length, and in the overlap length larger than 7 um, no latch-up occurs in the structure even the current density reaching several thousands of amperes / cm2. From Fig.4, it is noted that the latch-up current density increases sharply when the overlap length increases from 5 um to 6 um. It is suspected

Fig.2 The vectors of (a) the electron current and (b) the hole current of the LTGBT for n+ length of 7.5 um.

Fig.3. The hole current vectors at forward voltage of (a) 2 V and (b) 3 V for the LTGBT with n+ cathode length of 12 um.

Overlap length (µm)

Fig.4. Simulation results on the dynamic latch-up current density for the LTGBT at the different overlap lengths of the shorted n+ and p+ cathodes

that the rapid increase in latch-up current density is due to the electric field screening formed between the trench gate depletion region and the p+ cathode, which prevents holes to flow into the area underneath the n+ cathode. To verify this, latchup current density of these structures are simulated at different values of p+ cathode depth and a fixed overlap length of 6 um. The latch-up current density is found to be 1290, 1230, and 696 A/cm2 for the p+ cathode depths of 1.5 um, 1 um, and 0.5 um, respectively. The latch-up current density for the p+ cathode depth of 0.5 um is much lower than that for the depth of 1 um and 1.5 um. And further increasing the p+ depth from 1 um to 1.5 um does not show too much improvement on the latchup current density.

### IV. CONCLUSIONS

A conductivity modulated power transistor, called the LTGBT, was proposed. Its performance has been characterized using two dimensional numerical simulations. With the trench gate situated behind the cathode and the length of the n+ cathode near the channel minimized, holes can be collected by the cathode effectively without causing latchup even at high current level. The latch-up current density for the LTGBT exhibits more than 7.7 times improvement over the LIGBT. This improved latch-up performance is obtained at the expense of a slightly increase in the forward voltage. Furthermore, the dependence of the latch-up characteristics on the p+ cathode depth and the overlap length between the n+ and p+ cathode diffusions has been

elucidated. It is demonstrated that deeper p+ cathode depths and longer overlap lengths offer a higher latch-up current density. The maximum controllable latch-up current is not limited by the n+ cathode length, but by the space between the trench gate and the p+ cathode, which can be made quite small by increasing the overlap length between the n+ and p+ cathode diffusions.

#### **ACKNOWLEDGEMENT**

The authors would like to thank Technology Modeling Associates, Inc. for providing the device simulator MEDICI.

#### REFERENCE

- [1] M.R. Simpson, P.A. Gough, F.I. Hshieh, and V.Rumennik, "Analysis of the lateral insulated gate transistor", in 1985 IEEE IEDM Tech. Dig., PP.740-743

- [2] P.A. Gough, M.R. Simpson, and V.Rumennik, "Fast switching lateral insulated gate transistor", Proc. IEDM, PP.218-221 1986

- [3] J.K.O. Sin, "Lateral trench-gate bipolar transistors", United States Patent, Patent No. 5,227,653, issued July 13,1993

- [4] TMA MEDICI User's Manual, Technology Modeling Associates, Inc., Palo Alto, USA, 1992