# A COMPARISON BETWEEN NO-ANNEALED O<sub>2</sub>- AND N<sub>2</sub>O-GROWN GATE DIELECTRICS

P. T. Lai, J. P. Xu, and Y. C. Cheng

Department of Electrical and Electronic Engineering, the University of Hong Kong. Pokfulam Road, Hong Kong. Fax: (852) 2559 8738. Email: laip@hkueee.hku.hk.

Abstract - Qualities of oxynitrides prepared by annealing O2- and N2O-grown oxides in NO ambient are investigated. Harder oxide/Si interface, less charge trapping and higher charge-to-breakdown characteristics observed in NO-annealed N<sub>2</sub>O-grown (N2ONO) oxynitride than NO-annealed O2grown (O2NO) oxynitride. The involved mechanism lies in higher interfacial nitrogen concentration and total nitrogen content in N2ONO oxynitride than O2NO oxynitride for the same anneal temperature and time.

# I. INTRODUCTION

Currently, for satisfying the needs of scaled MOSFET's, high-quality thin gate dielectric is desired, because the properties of conventional SiO<sub>2</sub> films are not acceptable for these very small-sized transistors [1-3]. As an alternative dielectric, oxynitrides have considerable attention due to their superior performance and reliability properties over conventional SiO<sub>2</sub> [4-8]. However, NH<sub>3</sub>nitrided oxides suffer from hydrogen-related electron trapping problems [5-6] and N<sub>2</sub>Obased oxides require a much larger thermal budget for sufficient nitrogen incorporation [9-10]. To avoid these disadvantages of NH3 and N<sub>2</sub>O, nitric oxide (NO) is proposed as a dielectric-growth/anneal ambient to obtain high quality ultrathin dielectric films [8, 11-16]. Furthermore, NO-annealed process (an initial oxide grown in pure oxygen and then annealed in NO ambient) is preferred to prepare oxynitride with desired thickness in a reasonable growth time, considering the selflimiting nature of the growth process in NO ambient. Recently, our studies show that if the initial oxide is grown in N2O instead of O2 and then annealed in NO ambient, much better dielectric film can be obtained.

# II. EXPERIMENTAL

The MOS capacitors used in this study were fabricated on p-type (100) silicon wafers with a resistivity of 6-8  $\Omega$ -cm by a self-aligned n<sup>+</sup> polysilicon gate process. The initial gate oxide was grown to the same thickness in a conventional horizontal furnace in either dry O<sub>2</sub> or pure N<sub>2</sub>O ambient at 950 °C. Then, they were annealed in pure NO ambient at 950 °C for 30 min (denoted as O2NO for O2 growth and N2ONO for N2O growth, respectively). Control samples with same film thickness were thermally grown also at 950 °C in dry O<sub>2</sub> (denoted as OX). All gate oxides finally received an in situ N2 anneal at 950 °C for 20 min. Final oxide thickness (measured by C-V) was about 120 Å. Fowler-Nordheim constantcurrent stress with electron injection from the gate (negative gate bias) was used to evaluate the qualities of these gate dielectrics. In this case, the oxide/Si interface is the collecting electrode and the site of heaviest damage. The area of the capacitors were 10<sup>-4</sup> cm<sup>2</sup>. All measurements were carried out under light-tight and electrically shielded condition.

# III. RESULTS AND DISCUSSIONS

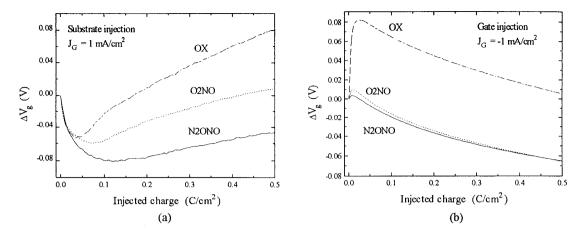

Electron and hole trapping characteristics of oxide bulk are examined by monitoring the change in gate voltage ( $\Delta V_G$ ) to maintain a contant current density of 1 mA/cm<sup>2</sup> from the substrate and gate injections. For both injections, as shown in Figs. 1 (a) and (b), initial hole trapping is followed by electron trapping. For substrate injection, the N2ONO sample

exhibits the highest hole trapping and lowest electron trapping, followed by the O2NO and OX samples. For gate injection, the two NOnitrided samples suffer from much lower initial hole trapping than the OX sample, with the N2ONO sample the lowest. On the other hand, electron trapping of the three samples looks almost identical. These results are very similar to that in [17], which studied the effect of interfacial nitrogen concentration Nint on electron and hole trappings. Hence, it is reasonable to conclude that the N2ONO oxynitride has a higher N<sub>int</sub> than the O2NO sample, indicating that double nitridation with N<sub>2</sub>O growth followed by NO anneal is effective in obtaining higher N<sub>int</sub> due to additional incorporation of nitrogen during N<sub>2</sub>O oxidation. The good oxidation resistance of N<sub>2</sub>O-grown oxide gives rise to very small thickness increase after NO annealing.

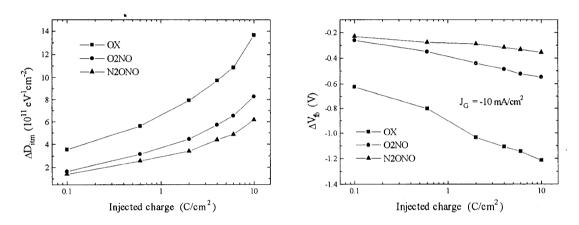

Hardness of the oxide/Si interface is evaluated by the increase of mid-gap interfacestate density ( $\Delta D_{itm}$ ) after a constant-current stress of -10 mA/cm<sup>2</sup> for different times. As shown clearly in Fig. 2, the two nitrided samples exhibit greatly suppressed creation of oxide/Si interface states compared to the OX due interfacial sample to nitrogen incorporation, with the N2ONO sample having better interface properties than the O2NO sample. This should be attributed to higher Nint in the N2ONO oxynitride, since more nitrogen incorporation near the oxide/Si interface gives more strong Si-N and N-O bonds and consequently a much harder interface.

Fig. 3 is the corresponding flat-band voltage shift  $\Delta V_{fb}$  under the same stress conditions as those used in Fig. 2. Like  $\Delta D_{itm}$ , the N2ONO sample is most resistant to  $V_{fb}$  shift. A negative shift in  $V_{fb}$  indicates hole trapping which is likely due to generated donor-like interface states [18] and bulk trapping near the oxide/Si interface. So, it can be believed that creation of hole traps at/near the oxide/Si interface is more effectively suppressed for the N2ONO oxynitride than the O2NO oxynitride based on the same reasons as for  $\Delta D_{itm}$ , although the N2ONO sample has more initial hole trapping for substrate injection, as shown in Fig. 1(a).

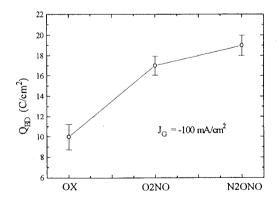

Presented in Fig. 4 is the measured charge-to-breakdown (Q<sub>BD</sub>) of the oxides under a constant-current stress of -100 mA/cm<sup>2</sup>. Improved Q<sub>BD</sub> in oxynitrides relative to thermal oxide is observed, with the N2ONO oxynitride as the best once again. From [19], higher trap generation in oxide and especially at the interface leads to lower QBD. So, different charge-to-breakdown characteristics of the three gate dielectrics should result from their different oxide and oxide/Si interface hardnesses, as described above. Also, hole trapping seems not to directly affect Q<sub>BD</sub> of oxynitrides, and this finding also agrees with the results in [17]. Therefore, it can be proposed that the larger amount of N in oxynitride near the interface is effective in considerably suppressing charge trapping and interface weakening.

#### IV. SUMMARY

Effects of NO-annealing on the qualities of O<sub>2</sub>- and N<sub>2</sub>O-grown oxides were investigated. It has been demonstrated that NO-annealed N<sub>2</sub>O-grown oxynitride has better properties than NO-annealed O2-grown oxynitride: harder oxide/Si interface, less charge trapping and higher charge-to-breakdown. These associated with higher interfacial nitrogen concentration and total nitrogen content in the former. Higher nitrogen concentration is also beneficial to resist dopant penetration through the gate oxide, especially in p<sup>+</sup> poly-gate p-MOSFET's of dual-gate CMOS technologies. Therefore, NO-annealed N2O-grown process could provide a highly reliable gate dielectric for MOS devices.

Acknowledgements -- This work is financially supported by the RGC and CRCG Research Grants, the University of Hong Kong.

# REFERENCES

- [1] K. Naruke, S. Taguchi, and M. Wada, in *IEDM Tech. Dig.*, 1988, p. 424.

- [2] P. Olivo, T. N. Ngyyen, and B. Ricco, *IEEE Trans. Electron Devices*, vol. 35, p. 2259, 1988.

- [3] R. Moazzami and C. Hu, in *IEDM Tech. Dig.*, 1992, p. 92.

- [4] T. Hori, H. Iwasaki, and K. Tsuji, *IEEE Trans. Electron Devices*, vol. 36, p. 340, 1989.

- [5] P. Pan, J. Appl. Phys., vol. 61, p. 284, 1986.

- [6] Z. Liu, H. -J. Wann, P. K. Ko, C. Hu, Y. C. Cheng, *IEEE Electron Device Lett.*, vol. 13, p. 402, 1992.

- [7] H. Fukuda, M. Yasuda, T. Iwabuchi, and S. Ohno, *IEEE Electron device Lett.*, vol. 12, p.587, 1991.

- [8] J. Ahn, W. Ting, and D. -L. Kwong, *IEEE Electron Device Lett.*, vol. 13, p. 117, 1992.

- [9] G. W. Yoon, A. B. Joshi, J. Kim, and D. L. Kwong, *IEEE Electron Device Lett.*, vol. 14, p. 179, 1993.

- [10]T. Hori, *Microelec. Eng.*, vol. 22, p. 245, 1993.

- [11]Z. -Q. Yao, H. B. Harrison, S. Dimitrijev, Y. T. Yeow, and D. Sweatman, *Appl. Phys. Lett.*, vol. 64, p. 3845, 1994.

- [12]Z. -Q. Yao, H. B. Harrison, S. Dimitrijev, and Y. T. Yeow, *IEEE Electron Device Lett.*, vol. 15, p. 516, 1994.

- [13]Y. Okada, P. J. Tobin, K. G. Reid, R. I. Hegde, B. Maiti, and S. A. Ajuria, *IEEE Trans. Electron Devices*, vol. 41, p. 1608, 1994.

- [14]L. K. Han, D. Wristers, J. Yan, M. Bhat, and D. L. Kwong, *IEEE Electron Device Lett.*, vol. 16, p. 319, 1995.

- [15]M. Bhat, J. Kim, J. Yan, G. W. Yoon, L. K. Han, and D. L. Kwong, *IEEE Electron Device Lett.*, vol. 15, p. 421, 1994.

- [16]Z. -Q. Yao, H. B. Harrison, S. Dimitrijev, and Y. T. Yeow, *IEEE Electron Device Lett.*, vol. 16, p. 345, 1995.

- [17]Y. Okada, P. J. Tobin, P. Rushbrook, and W. L. Dehart, *IEEE Trans. Electron Devices*, vol. 41, p. 191, 1994.

- [18]T. Hori, and H. Iwasaki, *IEEE Electron Device Lett.*, vol. 9, p. 168, 1988.

- [19]P. P. Apte, and K. C. Saraswat, *IEEE Electron Devices*, vol. 41, p. 1595, 1994.

Fig. 1 Change in gate voltage of MOS capacitors under a constant-current stress of 1 mA/cm<sup>2</sup>. (a) substrate injection and (b) gate injection.

Fig. 2 Increase in midgap interface state density  $(\Delta D_{itm})$  of MOS capacitors with different gate dielectrics under a constant-current stress of -10 mA/cm<sup>2</sup>.

Fig. 3 Flat-band voltage shift of MOS capacitors with injected charge under the same stress conditions as those in Fig. 2.

Fig. 4 Charge-to-breakdown ( $Q_{BD}$ ) of the three gate dielectrics measured under a constant-current stress of -100 mA/cm<sup>2</sup>.