ELECTRICAL ENGINEERING DEPARTMENT, UNIVERSITY OF HONG KONG.

# SEMINAR ON **CIRCUITS AND SYSTEMS**

Tuesday, July 31, 1979.

# Vice-Chancellor's Welcoming Speech for Seminar on Circuits and Systems on Tuesday, 31st July 1979.

It gives me great pleasure to welcome you all, this morning, to the opening of our Seminar on Circuits and Systems. Some of you are newcomers to the University of Hong Kong or even to Hong Kong itself. To them I would extend my good wishes for a very interesting and pleasant visit. But to all of you may I wish you a rewarding day with us here.

Today's Seminar focuses on an area of considerable interest to the modern Electrical Engineer, not least because the subject itself has reached a turning point. After a decade of abstraction, the field of circuits and systems, I understand, is being re-appraised and directed towards a more practical path. This Seminar, therefore, is both timely and pertinent. Amongst us this morning, we are particularly fortunate in having distinguished scholars of international repute, renowned for their pioneering work in the field and the publications arising therefrom. Their contributions to the Seminar will be extremely valuable and will provide us with food for thought for sometime to come. Their presence here will give us the benefit of personal contact and exchange of views - and this is a rare opportunity of which we will take full advantage.

Hong Kong is often considered by some as suffering from academic isolation. This criticism may have been more justified in the past, but now, with sophisticated communication and transportation networks, we are much better able to keep abreast of new trends and developments elsewhere. However, there can be no real substitute for direct discussion and debate, for "the meeting of minds". This Seminar, therefore, will serve in bringing practising engineers and academicians in Hong Kong closer to experts from overseas, and thus closer to the pulse of ideas. Some of our distinguished visitors have just returned from international conferences, on the same subject, in Tokyo and Taipei. With them they bring a wealth of new information for us to learn and ponder over. May I say how much we appreciate their presence here.

A warm welcome, too, to our colleagues from the Hong Kong industries. We are very glad indeed to have you with us. Your experience and expertise and your support for our work at the University, have long been valued by us, and we hope that this Seminar will strengthen the ties between us and that you will find time to visit us often.

The University is now embarking on new building projects for the Engineering Faculty. Do not judge us too harshly when we show you our present facilities, for in a few years we hope to proudly welcome you to our new Engineering building and to the rapid developments which by then will have taken place.

May I wish you all a very stimulating and enjoyable Seminar.

# A ONE-DAY SEMINAR ON CIRCUITS AND SYSTEMS

# July 31, 1979

# University of Hong Kong

# Morning Session

"Topological Analysis of Networks Some Recent Developments"

Dr. Shu-Park Chan Professor and Chairman Dept. of Elec. Engr. & Comp. Sci. University of Santa Clara Santa Clara, California 95053

- "Graphs and Teedback Amplifier Theory" Dr. Wai-Kai Chen Distinguished Professor Dept. of Electrical Engineering Ohio University Athens, Ohio 45701

- "Some Concepts for Hierarchical Layout of VLSI Circuits"

Dr. D. A. Mlynski Professor Dept. of Electrical Engineering University of Karlsruhe Karlsruhe, Germany

- 4. "Fuzzy Potentials in Network Problems" Dr. K. Onaga Professor Department of Circuits & Electrical Systems Engineering Hiroshima University Hiroshima City, Japan

- "Relevance of Network Theory to Models of Distributed/Parallel Processing" Dr. T. Murata

Professor Dept. of Information Engineering University of Illinois at Chicago Circle Chicago, Illinois 60680 Afternoon Session

- 6. "Accessibility of Large-Scale Electronic Circuits"

Dr. R. W. Liu Professor

Dept. of Electrical Engineering University of Notre Dame Notre Dame, Indiana 46556

- 7. "Block Implementation of Recursive Digital Filters"

Dr. S. K. Mitra Professor Dept. of Electrical Engineering University of California Santa Barbara, California 93106

- "A Characterization of the Invariance of Positivity for Functional Differential Equations"

Dr. I. W. Sandberg Bell Laboratories 600 Mountain Avenue Murray Hill, New Jersey 07974

9. "Linear Power Amplifiers in Microwave Radios"

Dr. C. C. Hsieh Manager Microwave Integrated Circuits Dept. Farinon Electric Co. San Carlos, California 94070

10. "Complete Stability of Non-reciprocal Nonlinear Networks"

Dr. Leon O. Chua Chaire de theorie des circuits et systems Ecole Polytechnique Federale de Lausanne 16 Chemin de Bellerive CH-1007 Lausanne Switzerland

# SHU-PARK CHAN

# TECHNICAL BIOGRAPHY

Shu-Park Chan was born in Canton, China, on October 10, 1929. He received his B.S. degree in electrical engineering from the Virginia Military Institute (V.M.I.) in 1955, the M.S. and Ph.D. degrees, both in electrical engineering, from the University of Illinois (U. of I.), Urbana-Champaign, in 1957 and 1963, respectively.

From 1957 to 1963, he taught at V.M.I. first as Instructor in Electrical Engineering and Mathematics and then as Assistant Professor of Mathematics.

On leave of absence from V.M.I., he was awarded a University Fellowship by U. of I. from 1959 to 1960 while studying toward the Ph.D. degree in electrical engineering at the University. He taught as Instructor in Electrical Engineering in that Department from 1960-61, and worked in the Coordinated Science Laboratories as Research Associate from 1961 to 1963 at the University.

Since February 1963, he joined the faculty in the Electrical Engineering and Computer Science Department at the University of Santa Clara, where he is presently Professor and Chairman. His major interests and publications have been in network and system theory, topological analysis and synthesis, computer-aided circuit design, and applied mathematics. He is author of *Introductory Topological Analysis of Electrical Networks* (Holt, Rinehart and Winston, 1969), co-author of *Analysis of Linear Networks and Systems: A Matrix-Oriented Approach with Computer Applications* (Addison-Wesley 1972) and *Introduction to the Applications of the Operational Amplifier* (Academic Cultural Co., 1974), and editor and major contributor of *Network Topology and Its Engineering Applications* (National Taiwan University Press, 1975).

Dr. Chan is a member of Tau Beta Pi, Eta Kappa Nu, Pi Mu Epsilon, Phi Kappa Phi, and Sigma Xi honorary societies and a member of American Association of the Advancement of Science, and of the American Society of Engineering Education. He is a Senior Member of the Institute of Electrical and Electronics Engineers (IEEE) and a past chairman of the Circuit Theory Group of the San Francisco Section IEEE. He is listed in American Men and Women of Science, Who's Who in America, International Scholars Directory, Dictionary of International Biography and Who's Who in the World.

Professor Chan is also president of the Chinese Arts and Culture Institute, and has been actively involved in promoting and organizing activities and projects relative to Chinese arts and culture in the Bay Area.

TOPOLOGICAL APPLICATIONS TO IC LAYOUT PROBLEMS

Yen-Son Huang

and Shu-Park Chan

Department of Electrical Engineering and Computer Science University of Santa Clara Santa Clara , California 95053

# 1. Design Rule Check [1-6]

# ABSTRACT

A topological approach based on oriented line segments is used to implement a set of logical and topological operations for IC layout manipulations which are useful in IC layout design rule check , IC layout resizing , and IC consistency check between the layout and the circuit/logical schematic.

# INTRODUCTION

Conventional integrated circuit (IC) design consists of preparing an initial circuit schematic and performing a circuit analysis using the computer simulation method. Once the designer is satisfied with the simulated performance , the circuit is transformed to an IC layout which is then digitized to obtain its computerized layout data base. The layout data base will be used to generate IC mask for fabrication. During the IC layout design , the size of transistors, resistors and capacitors are scaled and converted into area definition based on nominal circuit parameter values used for the circuit simulation. The sizes of the circuit components are adjusted to fit the IC layout design rules based on minimum spacing or width , relative element positions, and size requirements.

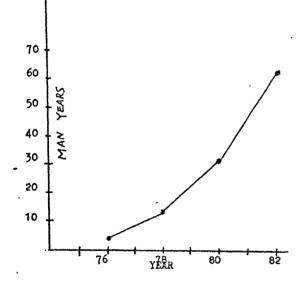

The design of an IC mask is time consuming and expensive because of the extensive checkings of the IC circuit and layout. Moreover , the amount of work to perform checkings will grow rapidly because the complexity of IC increases very rapidly as shown in figure 1. Thus, computer aids have been used extensively in the design and checking of IC masks to reduce the tedium involved in the consistency check between the layout and the circuit /logic schematic and the design rule check. Many computer-aided IC layout processing programs have been developed or developing in various type of companys such as semiconductor manufacturing companys , computer manufacturing companys , graphic application companys and data processing / service companys . Most of the programs are to implement a set of elementary operations from which a complete IC check can be generated . The elementary operations are listed as follows :

Also with National Semiconductor Corp., U S A

- Spacing Check Internal Spacing Check , External Spacing Check , Enclosure Spacing

Check , and Relational Spacing Check etc.

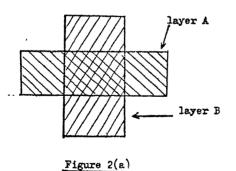

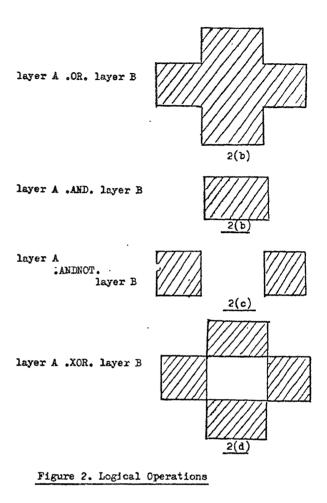

- (ii) Logical Operations OR , AND , ANDNOT , and XOR etc. (see figure 2.)

- (iii) Minimum Area Check

- (iv) Layout Resizing Expansion and Contraction.

- 2. IC Consistency Check between the Layout and the Circuit / Logic Schematic [9-12]

- Logical Operations OR , AND , ANDNOT , and XOR etc.

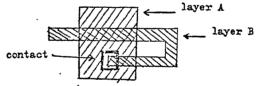

- (ii) Topological Operations : (see figure. 3.)

- (a) Identify regions each region may consist of a set of joint polygons,

- (b) Recognize two regions in two different layers are connected through contact(s), and

- (c) Recognize a region in one layer is surrounded (CONTAINED) by a region in the other layer, etc.

- (iii) Device Recognition recognize devices such as transistors, resistors and capacitors etc.

- (iv) Layout Resizing Expansion and Contraction.

- (v) Circuit Parameter Calculation resistances, capacitances and w/L 's of transistors etc.

According to the basic data item that the elementary operations operate on , there are several possible approaches shown below to implement these elementary operations.

- (2) Trapezoid (or Rectangle) approach 'the polygons are splitted into trapezoids (or rectangles) for data manipulations [6].

- (3) Vertex approach the vertices of polygons are used for data manipulations [3].

- (4) Line segment approach the polygons are splitted into line segments for data manipulations [5, 9].

- (5) Bit map approach the polygons are transformed into a bit map such that each bit corresponds

- to a unit of area and the areas enclosed by the polygons are represented by '1' and that not enclosed by '0' [2].

- (6) Symbolic approach the IC layout data base composed of a set of symbols such that each symbol represents a component or part of compont. The data manipulations can be on the - symbols [7-8].

In this paper, we are to present a topological approach based on oriented line segments to implement the algorithms for the logical operations and the topological operations.

#### II. DEFINITION

We shall first introduce the definition of oriented line segment (OLS) .

For each of line segments  $(v_i, v_{i+1})$ , between vertices  $v_i = (x_i, y_i)$  and  $v_{i+1} = (x_{i+1}, y_{i+1})$ , of an (n-1)-vertex clockwise polygon where i= 1, 2, ..., n-1, the OLS is defined as follows :

$0IS \triangleq \begin{cases} (\mathbf{v}_{i}, \mathbf{v}_{i+1}) \text{ with orientation 'up' if } \mathbf{y}_{i} < \mathbf{y}_{i+1} \\ (\mathbf{v}_{i+1}, \mathbf{v}_{i}) \text{ with orientation 'down' if } \mathbf{y}_{i} > \mathbf{y}_{i+1} \\ (\mathbf{v}_{i+1}, \mathbf{v}_{i}) \text{ with orientation 'horizontal-left'} \\ if \mathbf{y}_{i} = \mathbf{y}_{i+1} \text{ and } \mathbf{x}_{i} > \mathbf{x}_{i+1} \\ (\mathbf{v}_{i}, \mathbf{v}_{i+1}) \text{ with orientation 'horizontal-right'} \\ if \mathbf{y}_{i} = \mathbf{y}_{i+1} \text{ and } \mathbf{x}_{i} < \mathbf{x}_{i+1} \end{cases}$

In the  $(v_1, v_k)$  of an OIS, vertex v, is called the first vertex and  $v_k$  the second vertex of the OIS.

Hereafter, we will use  $\uparrow$ -OIS,  $\downarrow$ -OIS,  $\leftarrow$ -OIS, and  $\rightarrow$ -OIS to denote the OIS's with orientations 'up', 'down', 'horizontal-left', and 'horizontal-right' respectively. Moreover, for  $\uparrow$ -OIS and  $\downarrow$ -OIS, the y ordinate of the first vertex is always smaller than that of the second vertex. Thus, for convenience we will use (x<sub>1</sub>, y<sub>2</sub>) and (x<sub>1</sub>, y<sub>1</sub>) to denote the (x,y) coordinates of the first and the second vertex respectively.

# III. ALGORITHM OVERVIEW

The logical operations (OR , AND , ANDNOT , and XOR) operate on two layers (input layers) to generate another layer (output layer) and the topological operations operate on one, two or three layers to identify or recognize some topological properties. The algorithms for the logical operations and the topological operations are outlined in the following;

<u>Step 1.</u> For each of the input layers , create an OLS file which contains all the  $\uparrow$ -OLS and  $\downarrow$ -OLS of the polygons of the layer . Then sort the OLS file according to the ascending order of  $y_{4}$ , if the y 's are equal, sort according to their ascending order of  $x_{6}$ .

<u>Step 2</u>, Create a horizontal line y = h where h will start from the minimum  $y_i$ , go through all  $y_i$ 's,  $y_u$ 's and the y ordinates of the intesection points of OLS's, to the maximum  $y_u$  of the sorted OLS file. For each h, the set S, which contains all the OLS's intersecting with the line y = hand whose y > h, is sorted according to the following rule :

Sorting Rule at y = h

- Sort the OLS's in S according to the ascending order of their x ordinates at y = h; or

- (2) If their x ordinates at y = h are equal, sort the OLS's according to the ascending order of the (smallest) angle  $\theta$  measured in the clockwise direction from line y = h to the OLS's ; or

- (3) If their x ordinates at y = h and  $\theta$  are both equal, then sort the OLS's according to the orientation; i.e., 1-OLS's are ordered before  $\downarrow$ -OLS's.

Then , the logical operations perform the following two operations on the sorted S to generate the output layer .

- (1) <u>Grouping operation</u> this operation find the OLS pairs of the output layer between y = hand y = h' where

- (2) <u>Linking operation</u> this operation link the OLS pairs to form the polygons of the output layer.

The topological operations operate on the sorted S to find the topological properties listed in the Introduction .

In the following , we will discuss the Grouping operation , the Linking operation and the operations to identify the topological properties in detail.

#### IV. LOGICAL OPERATIONS

We will use the two variables I and J for counting and N identifying the OLS's pairs.

# 1. OR operation

- Set I = 0 and N = 0, Then, start to scan the sorted S.

- (ii) Fetch one OLS from the sorted S and perform

I←I+1 if it is a ↑-OLS or I←I-1 if

it is a ↓-OLS. Then ,

<u>Case 1.</u> If it is a  $\uparrow$ -OLS and I = 1, perform N  $\leftarrow$  N + 1 and assign it as the  $\uparrow$ -OLS of OLS pair N of the output layer.

Case 2. If it is a  $\downarrow$ -OIS and I = 0 , assign it as the  $\downarrow$ -OIS of OIS pair N .

For those cases other than the above two cases, go to (iii) .

- (iii) If all OLS's in S are fetched , stop ; otherwise , go to (ii) .

- 2. AND operation

- Set I = 0, J = 0 and N = 0, Then, start to scan the sorted S.

- (ii) Fetch one OLS from the sorted S . Perform I ← I+1 or I ← I-1 if it is a ↑-OLS or a ↓-OLS of the first input layer respectively, and perform J ← J+1 or J ← J-1 if it is a ↑-OLS or ↓-OLS of the second input layer respectively. Then ,

<u>Case 1.</u> If it is a 1-OIS of the first input layer, and I = 1 and  $J \neq 0$ ; or it is a 1-OIS of the second layer, and  $I \neq 0$  and J = 1; then perform  $N \leftarrow N + 1$  and assign it as the 1-OIS of OIS pair N..

<u>Case 2.</u> If it is a  $\frac{1}{7}$ -OLS of the first input layer, and I = 0 and J  $\neq$  0; or it is a  $\frac{1}{7}$ -OLS of the second input layer, and I  $\neq$  0 and J = 0; then assign it as the  $\frac{1}{7}$ -OLS of OLS pair N.

For those cases other than the above two cases , go to (iii) .

(iii) If all OLS's in S are fetched , stop ; otherwise , go to (ii) .

3. ANDNOT operation

- (i) Set I = 0, J = 0 and N = 0. Then start to scan the sorted S.

- (ii) Fetch one OLS from the sorted S . Perform I+I+1 or I+I-1 if it is a 1-OLS or ↓-OLS of the first input layer respectively, and perform J+J+1 or J+J-1 if it is a 1-OLS or ↓-OLS of the second input layer respectively. Then,

<u>Case 1.</u> If it is a  $\uparrow$ -OLS of the first input layer, I = 1 and J = 0; then perform N  $\leftarrow$  N+1 and assign it as the  $\uparrow$ -OLS of OLS pair N.

Case 2. If it is a  $\uparrow$ -OLS of the second input layer and I  $\neq$  0 and J = 1, then assign it as the  $\downarrow$ -OLS of OLS pair N.

<u>Case 3.</u> If it is a  $\downarrow$ -OLS of the second input layer and I  $\neq$  0 and J = 0, then perform N  $\leftarrow$  N+1 and assign it as the  $\uparrow$ -OLS of OLS pair N .

<u>Case 4.</u> If it is a  $\downarrow$ -OLS of the first input layer and I = 0 and J = 0, then assign it as the  $\downarrow$ -OLS of OLS pair N .

For those cases other than the above four cases, go to (iii) .

- (iii) If all OLS's in the sorted S are fetched , stop ; otherwise , go to (ii) .

- 4. XOR operation

- (i) Set I'=0, J=0 and N=0. Then start to to scan the sorted S.

- (ii) Fetch one OLS from the sorted S . Perform I← I+1 or I←I-1 if it is a ↑-OLS or ↓-OLS of the first input layer respectively, and

and perform  $J \nleftrightarrow J+1$  or  $J \twoheadleftarrow J-1$  if it is a 1-OLS or 4-OLS of the second input layer respectively . Then ,

<u>Case 1.</u> If it is a  $\uparrow$ -OLS of the first input layer and I = 1 and J =0 , or it is a  $\uparrow$ -OLS of the second input layer and I = 0 and J = 1; then perform N  $\leftarrow$  N+1 and assign it as the  $\uparrow$ -OLS of OLS pair N.

<u>Case 2.</u> If it is a  $\uparrow$ -OLS of the first input layer and I = 1 and J  $\neq$  0, or it is a  $\uparrow$ -OLS of the second input layer and I  $\neq$  0 and J = 1; then assign it as the  $\downarrow$ -OLS of OLS pair N.

Case 3. If it is a  $\downarrow$ -OLS of the first input layer and I = 0 and J  $\neq$  0, or it is a  $\downarrow$ -OLS of the second input layer and I  $\neq$  0 and J = 0; then N $\leftarrow$ N $\pm$ 1 and assign it as the  $\uparrow$ -OLS of OLS pair N.

Case 4. If it is a  $\downarrow$ -OLS of the first or second input layer and I=0 and J=0, then assign it as the -OLS of OLS pair N.

For those cases other than the above four cases, go to (iii) .

(iii) If all OLS's in the sorted S are fetched , stop; otherwise, go to (ii) .

#### V. LINKING OPERATION : -

Let S' be the set that contains all the OLS pairs at the current h and the previous h from the grouping operation . First , S' is sorted according to the Sorting Rule at y = h, then the Linking Operation will link the OLS's in S' at y = h as follows: Let N be a variable for identifying the link pair, then ,

- Set N = 1 and start to scan the sorted S'.

- (ii) Fetch two OLS's from the sorted S' and assign them to link pair N. The link pair are linked either by a common vertex or by a horizontal line segment of y = h.

- (iii) Set  $N \leftarrow N + 1$

- (iv) If all OIS's in the sorted S' are fetched, stop; otherwise, go to (ii).

#### VI. TOPOLOGICAL OPERATIONS

#### 1. Identify the regions in a layer

The OR operation can be applied to merge the joint polygons of the layer so that each polygon corresponds to a region .

Suppose that for each of the two input layers the operation to identify the regions in a layer has been performed such that each polygon corresponds to a region and is assigned a unique number. Then the operations for Recognizing the connections of two regions in two layers through contact(s) and Recognizing the CONTAIN relationship are as follows :

#### 2. Recognize the connections of two regions

Let I , J and K be the three variables for counting and  $p_1$  and  $p_2$  are for identifying the polygon num-

bers of the first and second input layers respectively .

- (i) Set I ,J and K equal to 0. Then start to scan the sorted S .

- (ii) Fetch one OLS from the sorted S . Perform  $I \leftarrow I+1$  or  $I \leftarrow I-1$  if it is a  $\uparrow$ -OLS or  $\downarrow$ -OLS of the first input layer respectively; or  $J \leftarrow J+1$  or  $J \leftarrow J-1$  if it is a  $\uparrow$ -OLS or  $\downarrow$ -OLS of the second input layer respectively; or  $K \leftarrow K+1$  or  $K \leftarrow K-1$  if it is a  $\uparrow$ -OLS or  $\downarrow$ -OLS of the contact layer. Then ,

<u>Case 1.</u> If it is a  $\uparrow$ -OLS of the first input layer , set p<sub>1</sub> equal to the polygon number from which it comes. Then if  $J \neq 0$  and  $K \neq 0$ , polygon p<sub>1</sub> of the first input layer and polygon p<sub>2</sub> of the second input layer are connected through contact.

<u>Case 2.</u> If it is a 1-OLS of the second input layer, set p, equal to the polygon number from which it comes. Then if  $I \neq 0$  and  $K \neq 0$ , polygon p, of the first input layer and polygon p, of the second input layer are connected through contact.

<u>Case 3.</u> If it is a  $\uparrow$ -OLS of the contact layer and I  $\neq$  0 and J  $\neq$  0, then polygon p, of the first input layer and polygon p<sub>2</sub> of the second input layer are connected through contact.

For those mases other than the above three cases , go to (iii) .

(iii) If all OLS's in the sorted S are fetched , stop ; otherwise , go to (ii) .

3. Recognize the CONTAINED relationship

Assume that any region in the first input layer is surrounded (CONTAINED) by a region in the second layer. We are to recognize which region in the first input layer is contained by which region in the second input layer.

- (i) Set I = 0 and J = 0. Then start to scan the sorted S.

- (ii) Fetch one OLS from the sorted S . Perform

I ← I+1 or I ← I-1 if is a ↑-OLS or ↓-OLS

of the first input layer, or perform

J ← J+1. or J ← J-1 if it is a ↑-OLS or ↓-OLS

of the second input layer respectively. Then

<u>Case 1.</u> If it is a  $\uparrow$ -OLS of the first input layer , set p, equal to the polygon number of the fet tched OLS .

<u>Case 2.</u> If it is a [-OLS of the second input layer and I = 0, then the polygon from which. it comes is contained by polygon  $p_2$  of the first input layer.

For those cases other than the above two cases, go to (iii)

(iii) If all OLS's in the sorted S are fetched, stop; otherwise, go to (ii).

VII. CONCLUSION

The oriented line segment approach has the following advantages :

1. The algorithm is simple because the well esta-

blished topological properties of polygons and its oriented line segments is applied. The algorithm implementation to handle the practical LSI layout is not difficult because each OLS is represented by a fixed length record and the system SORT can be used to pre-sort the OLS's in the sequence that is easy to be manipulated.

3. It is straight forward to obtain OLS's from the polygons and the Linking algorithm provides the backward capability to form polygons from the OLS's , thus the OLS approach can easily interface with the existing softwares such as pattern generation programs.

Even there are a great number of companies developing the layout processing programs, it is hard to find a paper that describes the algorithm in deep. The authors hope that this paper will stimulate the readers interesting in the area and becoming appreciated the concept of oriented line segments.

#### REFERENCES

- C. R. McCaw, " Unified Shapes Checker A Checking Tool for ISI," Proceedings of the 16th Design Automation Conference, San Diego, California, June 1979.

- P. Losleben and K. Thompson, "Topological Analysis for VISI Circuit," Proceedings of the 16th Design Automation Conference, San Diego, California, June 1979.

- 3. H. S. Baird, "Fast Algorithm for ISI Artwork Analysis," Proceedings of the 14th Design Automation Conference, New Orleans, Louisiana, June 1977.

- 4. P. Wilcox, H. Rombeek, and D. M. Caughey, " Design Rule Verification Based on One Dimensional Scans," Proceedings of the 15th Design Automat tion Conference, Las Vegas, Nevada, June 1978.

- 5. B. W. Lindsay, B. T. Preas, "Design Rule Checking and Analysis of IC Mask Design," Proceedings of 13th Design Automation Conference, San Francisco, California, June 1976.

- Topanga Data Systems, INC., " ICDS-DRC II and Admanced Features for the Design and Layout of Integrated Circuits," Topanga Data Systems, Inc. 1978.

- D. Gibson and S. Nance, "SLIC-Symbolic Layout of Integrated Circuits'" Proceeding of the 15th Design Automation Conference, Las Vegas, Nevada, June 1978.

- J. D. Williams," STICKS- A graphic Compiler for High Level Design," Hewlett-Packard Data Systems IC Laboratory, Cupertino, California , 1978.

- 9. B. T. Preas, B. W. Lindsay, and C. W. Gwyn," Automatic Circuit Analysis Based on Mask Information," Proceedings of the 13th Design Automation Conference, San Francisco, California, June 1976.

- L. Scheffer and R. Apte," LSI Design Verification Using Topology Extraction," Conference record of 12th Asilomar Conference on Circuits,

Systems & Computers, Pacific Grove, California, November 1978.

- 11. T. Akino, M. Shimode, Y. Kurashige and T. Neglehi, " Circuot Simulation and Timing Verification Based on MOS/ISI Mask Information," Proceedings of the 16th Design Automation Conference, San Diego, June 1979.

- M. F. Oakes, "The Complete VISI Design System, " Proceedings of the 16th Design Automation Conference, San Diego California, June 1979.

- 13. Y. S. Huang and S. P. Chan, " A Graph-Theoretic Approach to IC Layout Resizing," will be published in IEEE Transaction on Circuits and Systems.

Figure 1. Man years for Planning Drawing, Changing and Checking of Random Logic

Figure 3(a) A region consists of joint polygons

Figure 3(b). Two regions in two layers are connected by contact.

Figure 3(c). A region in one layer is surrounded by a region in the other layer

# WAI-KAI CHEN TECHNICAL BIOGRAPHY

Wai-Kai Chen (S' 61, M '61, SM '71, F '77) was born on December 23, 1936. He received the B.S. and the M.S. degrees in electrical engineering from Ohio University in 1960 and 1961, and the Ph.D. degree from University of Illinois in February 1964.

He was a Teaching Assistant at Ohio University from 1960 to 1961, and a University of Illinois Fellow and a C. T. Loo Fellow of China Institute in America at the University of Illinois in 1961 and 1962, respectively. He was a Research Assistant, then Research Associate, in the Coordinated Science Laboratory at the University of Illinois from 1962 to 1964. He was appointed as an Assistant Professor of Electrical Engineering at Ohio University in June 1964, and was promoted to Associate Professor in 1967 and Professor in 1971. During 1970-1971 Academic Year, he was a Visiting Associate Professor at Purdue University. He is the author of the books <u>Applied Graph Theory</u> (New York: American Elsovier and Amsterdam, The Netherlands: North-Holland, 1971), <u>Applied Graph Theory: Graphs and Electrical</u> <u>Networks</u> (Ibid, 2nd revised edition, 1976), <u>Theory and Design of Broadband</u> <u>Matching Networks</u> (London: Pergamon Press, 1976), and <u>Active Network and</u> <u>Feedback Amplifier Design</u> (Washington, D.C.: Hemisphere Publishing Corp. and New York: McGraw-Hill, 1979).

Dr. Chen is a recipient of the 1967 Lester R. Ford Award of the Mathematical Association of America. He received a Research Institute Fellow Award from Ohio University in 1972, an Outstanding Educator of America Award in 1973, and a Baker Fund Award in 1974 and also in 1978 from Ohio University. In 1975, he received an Excellence in Teaching Award from College of Engineering and Technology. He is a Fellow of American Association for the Advancement of Science. In 1978, he received the Distinguished Professor Award from Ohio University. He was Program Chairman of the 1979 International Colloquium on Circuits and Systems, Taiwan. Current, he is a Distinguished Professor of Electrical Engineering, Ohio University, and an Associate Editor of the IEEE Transactions on Circuits and Systems. For the Fall semester, 1979-1980, he is a Visiting Professor of Electrical Engineering, University of Hawaii at Manoa.

# Wai-Kai Chen

# Department of Electrical Engineering, Ohio University, Athens, Ohio, U.S.A.

#### ABSTRACT

The paper presents a unified summary of the relationships between network topology and feedback amplifier theory. Topological formulas for the evaluation of the elements of the return difference and the null return difference matrices are given.

#### INTRODUCTION

It is well known that Bode's concept of return difference plays an important role in the design of feedback amplifiers (1-3). Among the many important properties, it can be shown that the return difference is a generalization of the concept of the feedback factor of the ideal feedback model, that the sensitivity function of the amplifier is closely related to the return difference, and that the return difference is basic to the study of the stability of the feedback amplifier and to the determination of its transmission and driving-point properties.

Several important extensions and generalizations of Bode's return difference concept have been reported (4-7). Tasny-Tschiassny (4) introduced the concept of return-difference matrix. The results so obtained are applicable to linear feedback networks that possess a multiplicity of physical feedback loops. Truxal (6) introduced the concept of the null return difference, which is shown to be useful in measurement situations and in the computation of the sensitivity. The extension of the null return difference to the concept of the null return-difference matrix was given by Sandberg (5) and Hakim (7), who demonstrated its use in the evaluation of the closed-loop gain and the drivingpoint impedance of a multiple-loop feedback network. Needless to say, these concepts have been modified and elaborated upon by many workers (8-17).

It was shown by Chen (18, 19) that although the return difference and the null return difference are not invariant with respect to the general transformations of the reference frame, they are invariant for the most common and important types of feedback networks. These results have been extended and generalized to the multiple-loop feedback networks by Elsherif and Chen (20).

In the present paper, we present a unified summary of many of these results, and indicate how the elements of the return-difference and the null return-difference matrices can be expressed in terms of the directed-tree and directed-two-tree admittance products in the associated digraph.

# THE FIRST- AND SECOND-ORDER COFACTORS

Let  $\underline{Y}$  be the indefinite-admittance matrix of a feedback amplifier N. Denote by  $\underline{Y}_{ij}$  the submatrix obtained from  $\underline{Y}$  by deleting the row i and column j. In a similar way,  $\underline{Y}_{TP}$ , sq denotes the submatrix derived from  $\underline{Y}$  by deleting the rows r and s and columns p and q. The <u>first</u>- and the <u>second</u>-<u>order cofactors</u> of the elements of  $\underline{Y}$ , which is of order n, are the scalar quantities defined by

$$Y_{ij} = (-1)^{i+j} \det Y_{ij}$$

(1)

$$Y_{rp,sq} = sgn (r-s) sgn (p-q) (-1)^{r+p+s+q}$$

$$\det Y$$

(2)

respectively, where r, s, p, q  $\leq n$ ; and sgn u = + 1 if u > 0, sgn u = - 1 if u < 0, and sgn 0 = 0. It is well known that <u>Y</u> is an equicofactor matrix (21) meaning that

$$\mathbf{Y}_{ij} = \mathbf{Y}_{uv} \tag{3}$$

for all i, j, u and v.

In a feedback network N, the <u>general return</u> <u>difference</u>  $F_k(x)$  of N with respect to a network element x for a general reference value k is defined as the ratio of the two functional values assumed by the network determinant under the condition that the element x assumes its nominal value and the condition that the element x assumes the value k. This gives

$$F_{k}(s) = Y_{ij}(x)/Y_{ij}(k),$$

(4)

where we have exhibited the importance of the element x by writing  $Y_{ij} = Y_{ij}(x)$ . For k = 0, we write  $F_0(x) = F(x)$ , which becomes the ordinary return difference.

The concept of null return difference is found to be very useful in measurement situations and in the computation of the sensitivity for the feedback amplifiers (2, 6).

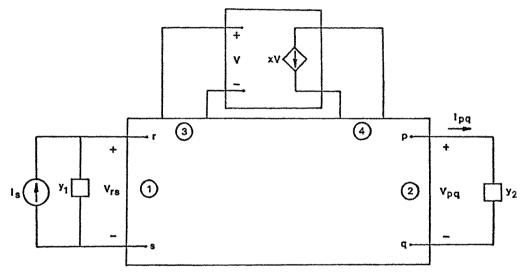

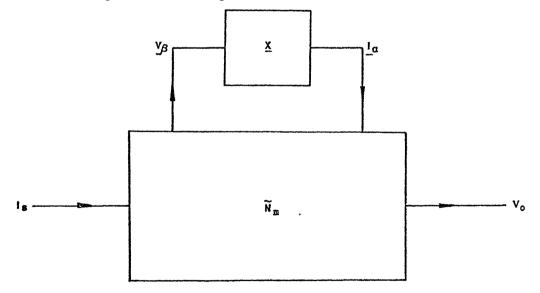

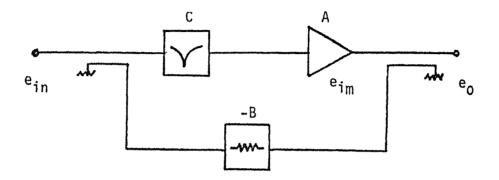

In the literature, the null return difference  $\widehat{F}(x)$  with respect to a voltage-controlled current source I = xV for the zero reference value is defined to be one plus the negative voltage appearing at the controlled source is replaced by an independent current source of x amperes and when the input current of the feedback amplifier is adjusted so that its output current is identically zero. Referring to the general configuration of a feedback amplifier as shown in Fig. 1, let us designate the input and output terminals as shown. As demonstrated by Chen (22), the null return difference

can be expressed as the ratio of the two functional values assumed by a second-order cofactor of the elements of the indefinite-admittance matrix  $\underline{Y}$  under the condition that the element x assumes its nominal value and the condition that the element x assumes the value k, that is

$$\widehat{F}_{k}(x) = Y_{rp,sq}(x)/Y_{rp,sq}(k), \qquad (5)$$

where, as before, we write  $Y_{rp,sq}$  as  $Y_{rp,sq}(x)$ . Since

$$Y_{rp,sq}(x) = -Y_{sp,rq}(x) = -Y_{rq,sp}(x),$$

(6)

the null return difference  $\hat{F}_k(x)$ , as given in (5), is independent of the choice of the reference potentials for the input and output ports. In other words, there is no need to specify the terminal labels of the input and output ports; only the identification of these ports is required for the computation of  $\hat{F}_k(x)$ .

# MULTIPLE-LOOP FEEDBACK NETWORKS

The extension of the scalar return difference and null return difference for a single loop feedback amplifier to the return-difference matrix and the null return-difference matrix for a multipleloop feedback amplifier will be considered in this section.

In a multiple-loop feedback network  $N_m$ , let the elements of interest be represented by a rectangular matrix  $\underline{X}$ , which can either be a transferadmittance matrix or a driving-point admittance matrix characterized by

$$I_{\alpha} = \underline{X} V_{\beta}, \qquad (7)$$

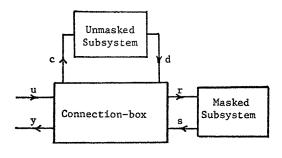

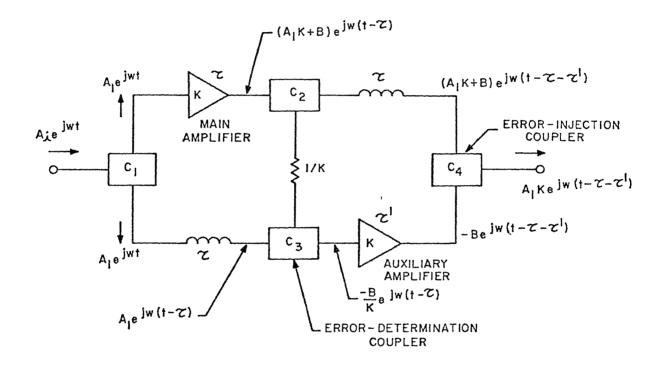

where  $\underline{X}$  is of order  $\overline{q}$  by p. If  $\underline{X}$  is a transferadmittance matrix of the controlling parameters of the voltage-controlled current sources, Vg represents a p-dimensional vector of the controlling voltages and  $I_{\underline{\alpha}}$  a q-dimensional vector of controlled current sources. If  $\underline{X}$  represents a drivingpoint admittance matrix,  $I_{\underline{\alpha}}$  and Vg are of the same dimension, p = q, and they represent current and voltage vectors of a p-port network. The matrix  $\underline{X}$  is important in terms of its effects to the whole system and is imbedded in the rest designated by  $\widehat{N}_{\underline{m}}$  as shown in the block diagram of Fig. 2, where  $I_{\underline{S}}$  denotes the input current and  $V_0$  the output voltage of  $N_{\underline{m}}$ . Since the network  $\widehat{N}_{\underline{m}}$  is linear, it can be characterized by

$$\underline{V}_{\beta} = \underline{AI}_{\alpha} + \underline{BI}_{s}, \qquad (8a)$$

$$V_{o} = \underline{CI}_{\alpha} + DI_{s}, \qquad (8b)$$

where <u>A</u>, <u>B</u>, <u>C</u> and D are transfer-impedance matrices of order  $p \ge q$ ,  $p \ge 1$ ,  $1 \ge q$ , and  $1 \ge 1$ , respectively.

Denote by 1<sub>p</sub> the identity matrix of order p. Then the square matrix

$$\underline{F}(\underline{X}) = 1 - \underline{AX}$$

(9)

is called the <u>return difference</u> <u>matrix</u> of  $N_m$  with respect to the matrix  $\underline{X}$ , and is a direct generalization of Bode's scalar return difference (1) with respect to a single element x.

The <u>null return</u> difference <u>matrix</u> of N<sub>m</sub> with

respect to  $\underline{X}$  is defined by the square matrix

$$\underline{\widehat{F}}(\underline{X}) = \underline{1}_{p} - \underline{\widehat{A}X}, \qquad (10)$$

$$\underline{\hat{A}} = \underline{A} - (1/D)\underline{BC}, \qquad (11)$$

provided that  $D \neq 0$ .

where

As shown by Kuh (9), the closed-loop transfer impedance  $w(\underline{X})$ , defined as the ratio of the output voltage  $V_0$  to input current  $I_s$ , can be expressed in a very compact way by making use of the return difference and null return difference matrices:

$$f(\underline{X}) = \left[ w(\underline{0}) \det \underline{\widehat{F}}(\underline{X}) \right] / \left[ \det \underline{F}(\underline{X}) \right].$$

(12)

The sensitivity function  $S(x_{ij})$ , which is defined as the ratio of the fractional change in a transfer function  $w(\underline{X})$  to the fractional change in an element  $x_{ij}$  of  $\underline{X}$ , can be written as

$$S(x_{ij}) = \frac{\det \underline{F}(\underline{X}) \Big|_{x_{ij}=0}}{\det \underline{F}(\underline{X})} \left[1 - \frac{w(\underline{X}) \Big|_{x_{ij}=0}}{w(\underline{X})}\right]. (13)$$

# TOPOLOGICAL FORMULAS

In this section, we present topological formulas for the evaluation of feedback parameters in terms of the products of admittances associated with the directed trees and directed two-trees in the associated digraph of the feedback amplifier.

# The Digraph

For a given feedback amplifier N, let  $G(\underline{Y})$  be the n-node directed graph, called the <u>digraph</u> of N associated with its indefinite-admittance matrix

$$\underline{\mathbf{Y}} = \left[ \mathbf{y}_{ij} \right], \qquad (14)$$

which is of order n, as follows. There is an edge directed from node i to node j with weight -  $y_{ij}$ ,  $i \neq j$ , in  $G(\underline{Y})$  if and only if  $y_{ij} \neq 0$ . We remark that the diagonal elements of  $\underline{Y}$  have no direct bearing on the construction of  $G(\underline{Y})$ . A careful study of this rule indicates that  $G(\underline{Y})$  can be greatly simplified if we agree that an undirected edge stands for a pair of oppositely directed edges such that the weight (admittance) associated with each directed edge in the pair is the same as that of the undirected edge. With this simplification, it is clear that the resulting  $G(\underline{Y})$  is a <u>composite graph</u>, and for most practical and commonly used networks,  $G(\underline{Y})$  can easily be obtained from the equivalent network of the feedback amplifier N by inspection. For a detailed account of this result and all the variations and ramifications, the reader is referred to Chen (21). We shall further agree that the directed edges in the composite graph  $G(\underline{Y})$  will be called the <u>active edges</u>, and the undirected edges the <u>passive edges</u>.

A directed tree with reference node r in  $G(\underline{Y})$ denoted by  $t_r$ , is a tree in which each of its active edges, if they exist, is directed toward the reference node r in the unique path defined by the active edge in the tree. In particular, trees consisting only of passive edges are also directed trees. A <u>directed</u> <u>two-tree</u> with reference nodes i and j, denoted by  $t_{1,j}$ , is a two-tree separating the nodes i and j, each of its components being a directed tree with reference node i or j in some subgraph of  $G(\underline{Y})$ . Also, denote by  $t_{\underline{1}u, \underline{j}v}$  a directed two-tree  $t_{i, \underline{j}}$  in which nodes i and u are in one component and nodes j and v in the other component; the first subscripts i and j being the reference nodes. For a subgraph g of  $G(\underline{Y})$ , denote by f(g) the product of the weights associated with the edges of g with  $f(\beta) = 0$ ,  $\beta$  being the null graph.

With these preliminaries, we can now state the following known results, whose proof can be found in Chen (21):

$$Y_{uv} = T_k = \sum_{t_k} f(t_k),$$

(15)

$$Y_{rp,sq} = W_{rp,sq} = T_{rp,sq} - T_{rq,sp}, \qquad (16)$$

where the choice of the reference node  $\boldsymbol{k}$  is arbitrary and

$$T_{rp,sq} = \sum_{t_{rp,sq}} f(t_{rp,sq}).$$

(17)

The Return Difference

Substituting (15) in (4) yields the desired formula for the return-difference function

$$F_{k}(x) = T_{i}(x)/T_{i}(k),$$

(18)

where  $T_{i} = T_{i}(x).$

The Null Return Difference

Combining (5) and (16) gives

$$\widehat{F}_{k}(\mathbf{x}) = \mathbf{W}_{rp,sq}(\mathbf{x})/\mathbf{W}_{rp,sq}(\mathbf{k}), \quad (19)$$

-

where  $W_{rp,sq} = W_{rp,sq}(x)$ .

-

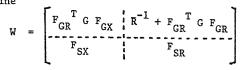

# The Return Difference Matrix

In this section, we present topological formulas for the evaluation of the elements of the return difference matrix.

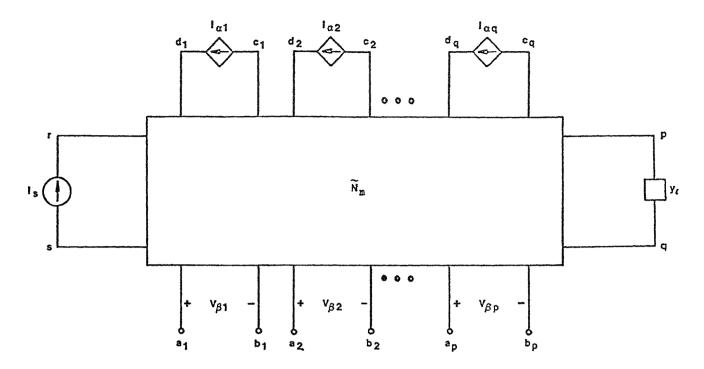

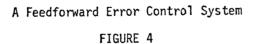

Referring to the general configuration of Fig. 3, the controlled sources can be represented by the equation

$$\begin{bmatrix} I_{\alpha 1} \\ I_{\alpha 2} \\ \vdots \\ I_{\alpha q} \end{bmatrix} = \begin{bmatrix} x_{11} & x_{12} & \cdots & x_{1p} \\ x_{21} & x_{22} & \cdots & x_{2p} \\ \vdots & \vdots & \vdots & \vdots \\ x_{q1} & x_{q2} & \cdots & x_{qp} \end{bmatrix} \begin{bmatrix} v_{\beta 1} \\ v_{\beta 2} \\ \vdots \\ v_{\beta p} \end{bmatrix}.$$

(20)

As indicated in (8a), A is the matrix relating the controlling voltage vector  $V_{\beta}$  to the controlled current vector  $I_{\alpha}$  after the input excitation  $I_s$  has been set to zero. Under this situation, the (i,j)-element of AX is equal to the voltage  $V_{\beta 1}$  appearing at the ith controlling branch of Fig. 3 when the controlled current sources  $I_{\alpha k}$  (k = 1, 2, ..., q)

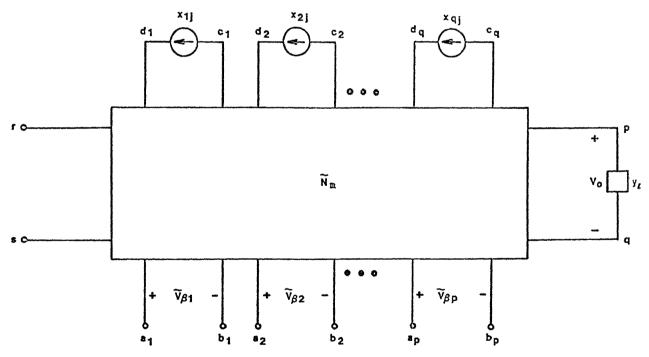

have been replaced by the independent current sources of strengths  ${\bf x}_{k\,j},$  as depicted in Fig. 4. Thus, with

$$\underline{F}(\underline{X}) = \begin{bmatrix} F_{ij} \end{bmatrix}$$

(21)

we have for the jth column elements of  $\underline{F}(\underline{X})$

$$F_{ij} = -\tilde{V}_{\beta i}, \quad i \neq j, \quad (22a)$$

$$= 1 - \tilde{V}_{\beta i}, \quad i = j.$$

(22b)

Since the network is linear, the voltage  $\widetilde{v}_{\beta j}$  due to the independent current sources  $x_{kj}$  can be obtained by considering each source separately, and the result is given by

$$Y_{uv}(\underline{0})\tilde{V}_{\beta i} = \sum_{k=1}^{q} x_{kj} Y_{d_k a_i, c_k b_i}(\underline{0}).$$

(23)

Appealing to (15) and (16), we have for  $i \neq j$

$$T_{\underline{m}}(\underline{0})F_{\underline{i}\underline{j}} = \sum_{k=1}^{\underline{q}} x_{k\underline{j}}W_{\underline{d}_{k}b_{\underline{i}}}, c_{k\underline{a}\underline{i}}(\underline{0}); \qquad (24)$$

and for i = j

$$T_{\underline{m}}(\underline{0})F_{\underline{i}\underline{i}} = T_{\underline{m}}(\underline{0}) + \sum_{k=1}^{q} x_{k\underline{i}} W_{\underline{k}} b_{\underline{i}}, c_{k} a_{\underline{i}} (\underline{0}).$$

(25)

In the special situation where  $\underline{X}$  is diagonal, which occurs most often in practice, (24) and (25) reduce to

$$\mathbf{f}_{\mathbf{m}}(\underline{\mathbf{O}})\mathbf{F}_{\mathbf{i}\mathbf{j}} = \mathbf{x}_{\mathbf{j}\mathbf{W}_{\mathbf{d}_{\mathbf{j}}\mathbf{b}_{\mathbf{i}}}, \mathbf{c}_{\mathbf{j}}\mathbf{a}_{\mathbf{i}}}^{\mathbf{a}}(\underline{\mathbf{O}})$$

(26)

for  $i \neq j$ , and

$$T_{m}(\underline{O})F_{ii} = T_{m}(\underline{O}) + x_{ii}W_{d_{i}b_{i}}, c_{ia_{i}}(\underline{O})$$

$$= T_{m}(\underline{X}^{ii}), \qquad (27)$$

where  $\underline{X}^{ij}$  is the matrix derived from  $\underline{X}$  by setting all of its elements to zero except  $x_{ij}$ . Thus,  $\underline{X}^{ij}$ is the matrix consisting only of zeros except the ith row and jth column element, which is  $x_{ij}$ . We remark that directed trees and two-trees in

We remark that directed trees and two-trees in (24)-(27) are to be evaluated in the digraph obtained from  $G(\underline{Y})$  by setting to zero all the weights corresponding to the elements of  $\underline{X}$ . If  $\underline{X}$  is the matrix of the controlling parameters, the resulting digraph is simply the graph representing the feedback network when the input excitation and all the controlled sources have been removed, and the directed trees and two-trees become the ordinary trees and two-trees.

# The Null Return Difference Matrix

, The null return difference matrix is found to be very useful in measurement situations and in the computation of the sensitivity for the multipleloop feedback amplifiers (2, 23). In the following, we present topological formulas for the evaluation of its elements.

The null return difference matrix  $\hat{F}(X)$ , as defined in (10), is the return difference matrix with respect to X when the input excitation I<sub>S</sub> is adjusted so that the output voltage V<sub>0</sub> of Fig. 4 (I<sub>S</sub> is not explicitly shown) is identically zero. Thus,  $\hat{A}$  is the matrix relating the controlling voltage vector  $V_\beta$  to the controlled current vector  $\underline{L}a$  when the input excitation  $I_S$  is adjusted so that the output voltage  $V_0$  is identically zero. Under this situation, to compute the jth column elements of  $\underline{A}X$ , we replace the controlled current sources  $I_{CK}$  (k = 1, 2, ..., q) in Fig. 3 by the independent current sources of strengths  $x_{kj}$ , as depicted in Fig. 4, and then adjust the input excitation  $I_S$  so that the output voltage  $V_0$  is identically zero. The voltage  $V_{\beta i}$  appearing at the ith controlling branch is the (i,j)-element of  $\underline{A}X$ . Let the desired input excitation be designated by  $I_{Sj}$  (j = 1, 2, ..., p). Applying the principle of superposition, the output voltage  $V_0$  is given by

$$Y_{uv}(\underline{0})V_{o} = I_{s}Y_{rp,sq}(\underline{0}) + \sum_{k=1}^{q} x_{kj}Y_{d_{k}p,c_{k}q}(\underline{0}). \quad (28)$$

Setting  $V_0 = 0$  and using (16), the desired input excitation can be computed by the formula

$$\mathbf{I}_{sj} = \sum_{k=1}^{q} \mathbf{x}_{kj} \mathbf{W}_{d_k q, c_k p}(\underline{0}) / \mathbf{W}_{rp, sq}(\underline{0}).$$

(29)

The voltage appearing at the ith controlling branch is found to be

$$Y_{uv}(\underline{0})\tilde{V}_{\beta i} = I_{sj}Y_{ra_{i},sb_{i}}(\underline{0}) + \sum_{k=1}^{q} x_{kj}Y_{d_{k}a_{i},c_{k}b_{i}}(\underline{0}).$$

(30)

Let

.

$$\underline{\hat{\mathbf{F}}}(\underline{\mathbf{X}}) = \begin{bmatrix} \widehat{\mathbf{F}}_{ij} \end{bmatrix}.$$

(31)

Then from (30) in conjunction with (15) and (16), we obtain

$$\dot{\mathbf{T}}_{\mathbf{m}}(\underline{\mathbf{0}})\hat{\mathbf{F}}_{\mathbf{j}} = \sum_{k=0}^{\mathbf{q}} \mathbf{x}_{kj} \mathbf{w}_{d_k \mathbf{b}_{\mathbf{j}}, \mathbf{c}_k \mathbf{a}_{\mathbf{j}}} (\underline{\mathbf{0}}), \quad \mathbf{i} \neq \mathbf{j}, \quad (32)$$

$$T_{\underline{m}}(\underline{0})\hat{F}_{\underline{i}\underline{i}} = T_{\underline{m}}(\underline{0}) + \sum_{k=0}^{q} x_{k\underline{i}} \mathbb{W}_{d_{k}b_{\underline{i}},\widehat{c}_{k}a_{\underline{i}}}(\underline{0}), \quad (33)$$

.

where  $x_{0j} = I_{sj}$ ,  $c_0 = s$  and  $d_0 = r$ .

In the special situation where  $\underline{X}$  is diagonal, (32) and (33) reduce to

$$\mathbf{T}_{\mathbf{m}}(\underline{\mathbf{0}})\hat{\mathbf{F}}_{\mathbf{i}\mathbf{j}} = \mathbf{I}_{\mathbf{s}\mathbf{j}} \mathbf{W}_{\mathbf{r}\mathbf{b}_{\mathbf{i}},\mathbf{s}\mathbf{a}_{\mathbf{i}}}(\underline{\mathbf{0}}) + \mathbf{x}_{\mathbf{j}\mathbf{j}} \mathbf{W}_{\mathbf{d}_{\mathbf{j}}\mathbf{b}_{\mathbf{i}},\mathbf{c}_{\mathbf{j}}\mathbf{a}_{\mathbf{i}}}(\underline{\mathbf{0}}) \quad (34)$$

for  $i \neq j$ , and from (29) and (30)

$$\hat{\mathbf{F}}_{ii} = 1 - \left[\mathbf{I}_{si}\mathbf{Y}_{ra_{i}}, sb_{i}}(\underline{0}) + \mathbf{x}_{ii}\mathbf{Y}_{d_{i}a_{i}}, c_{i}b_{i}}(\underline{0})\right]/\mathbf{Y}_{uv}(\underline{0})$$

$$= 1 + \mathbf{x}_{ii}\dot{\mathbf{Y}}_{rp, sq}(\underline{0})/\mathbf{Y}_{rp, sq}(\underline{0}), \qquad (35)$$

where  $\dot{Y}_{rp, sq}(\underline{0})$  denotes the partial derivative of  $Y_{rp, sq}(\underline{X})$  with respect to the element  $x_{ii}$  evaluated at  $\underline{X} = \underline{0}$ . Using  $\dot{X}^{ii}$  as defined in (27), it is not difficult to show that  $Y_{rp, sq}(\underline{X}^{ii})$  can be expanded as

$$Y_{rp,sq}(\underline{X}^{-}) = Y_{rp,sq}(\underline{0}) + X_{ii}Y_{rp,sq}(\underline{0}). \quad (36)$$

Substituting (36) in (35) yields

$$\hat{F}_{ii} = W_{rp,sq}(\underline{X}^{ii})/W_{rp,sq}(\underline{0}).$$

(37)

CONCLUSIONS

In the paper, we have presented a unified summary of the relationships between network topology and feedback amplifiers. Topological formulas for the evaluation of the elements of the return difference matrix and the null return difference matrix in terms of the sums of the directed-tree and directed-two-tree admittance products are given. The significance of these formulas is that it not only provides a short-cut for the evaluation of the feedback matrices, but also gives an insight into the behavior of the feedback amplifier under consideration.

#### REFERENCES

- H. W. Bode, "Network Analysis and Feedback Amplifier Design," Princeton, NJ: Van Nostrand, 1959.

- (2) E. S. Kuh and R. A. Rohrer, "Theory of Linear Active Networks," San Francisco, CA: Holden-Day, 1967.

- Day, 1967. (3) S. S. Haykin, "Active Network Theory," Reading, MA: Addison-Wesley, 1970.

- (4) L. Tasny-Tschiassny, "The Return Difference Matrix in Linear Networks," PROC. IEE (London), Vol. 100. Pt. IV. pp. 39-46: Jan. 1953.

- Vol. 100, Pt. IV, pp. 39-46: Jan. 1953.

(5) I. W. Sandberg, "On the Theory of Linear Multi-Loop Feedback Systems," BELL SYST. TECH. J., Vol. 42, pp. 355-382: Mar. 1963.

(6) J. G. Truxal, "Automatic Feedback Control Sys-

- (6) J. G. Truxal, "Automatic Feedback Control System Synthesis," New York: McGraw-Hill, 1955.

(7) S. S. Hakim, "Multiple-Loop Feedback Circuits,"

- (7) S. S. Hakim, "Multiple-Loop Feedback Circuits," PROC. IEE (London), Vol. 110, pp. 1955-1959: Nov. 1963.

- (8) R. F. Hoskins, "Definition of Loop Gain and Return Difference in Transistor Feedback Amplifiers," PROC. IEE (London), Vol. 112, pp. 1995-2001: Nov. 1965

- (9) E. S. Kuh, "Some Results in Linear Multiple Loop Feedback Systems," in PROC. 1ST ANN. AL-LERTON CONF. SYSTEMS AND CIRCUIT THEORY, University of Illinois, Urbana, pp. 471-487: Nov. 1963.

- (10) S. S. Hakim, "Aspects of Return-Difference Evaluation in Transistor Feedback Amplifiers," PROC. IEE (London), Vol. 112, pp. 1700-1704: Sept. 1965.

- (11) S. S. Hakim, "Return-Difference Measurement in Transistor Feedback Amplifiers," PROC. IEE (London), Vol. 112, pp. 914-915: May 1965.

(12) A. G. J. MacFarlane, "Return-Difference and

- (12) A. G. J. MacFarlane, "Return-Difference and Return-Ratio Matrices and Their Use in Analysis and Design of Multivariable Feedback Control Systems," PROC. IEE (London), Vol. 118, pp. 946-947: July 1971.

(13) A. F. Arbel, "Identification of the Return Dif-

- (13) A. F. Arbel, "Identification of the Return Difference Matrix of a Multivariable Linear Control System, in Terms of Its Inverse Closed-Loop Transfer Matrix," INT. J. CIRCUIT THEORY AND APPL., Vol. 1, pp. 187-190: June 1973.

- (14) A. F. Arbel, "Return Ratio and Sensitivity Computation for Multivariable Control Systems and Feedback-Stabilized Multiple Amplifier Active Circuits," INT. J. CIRCUIT THEORY AND APPL., Vol. 1, pp. 191-199: June 1973.

(15) A. G. J. MacFarlane, "Return-Difference Matrix

- (15) A. G. J. MacFarlane, "Return-Difference Matrix Properties for Optimal Stationary Kalman-Bucy Filters," PRCC. IEE (London), Vol. 118, pp. 373-376: Feb. 1971.

- (16) W. K. Chen, "Invariance and Mutual Relations of the General Null-Return-Difference Functions," in PROC. 1974 EUROPEAN CONF. CIRCUIT THEORY AND DESIGN, IEE Conf. publ. no. 116, pp. 371-376: July 1974.

- (17) J. H. Mulligan, Jr., "Signal Transmission in Non-Reciprocal Systems," in PROC. SYMP. ON AC-TIVE NETWORKS AND FEEDBACK SYSTEMS, Polytechnic Institute of Brooklyn, pp. 125-153: Apr. 1960. (18) W. K. Chen, "Graph-Theoretic Considerations on

- the Invariance of Return Difference," J. FRANK-

- LIN INST., Vol. 298, pp. 81-100: Aug. 1974 (19) W. K. Chen, "Graph-Theoretic Considerations on the Invariance of the Return Difference," in PROC. INT. SYMP. CIRCUITS AND SYSTEMS, IEEE catalog no. 74CH0818-5 CAS, pp. 319-323: Apr. 1974.

- (20) H. M. Elsherif and W. K. Chen, "The Return (20) H. H. Elsherif and W. K. Chen, "The Return Difference Matrix in Multiple-Loop Feedback Systems," in PROC. 17TH MIDWEST SYMP. ON CIR-CUITS AND SYSTEMS, University of Kansas, law-rence, Kansas, pp. 95-103: Sept. 1974.

(21) W. K. Chen, "Applied Graph Theory," New York: American Elsevier, and Amsterdam, The Nether-New W. W. Walter, 2007.

- lands: North-Holland, 1971.

- (22) W. K. Chen, "Indefinite-Admittance Matrix For-mulation of Feedback Amplifier Theory," IEEE TRANS. CIRCUITS SYST., Vol. CAS-23, pp. 498-

- 505: Aug. 1976. (23) W. K. Chen, "Active Network and Feedback Amplifier Theory," New York: McGraw-Hill, and Washington, D.C.: Hemisphere Publishing Corp., 1979.

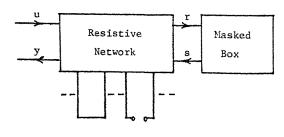

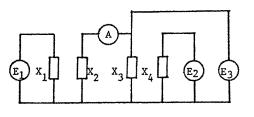

Fig. 1. General Configuration of a Feedback Amplifier Network.

Fig. 2. The General Configuration of a Multiple-Loop Feedback Amplifier.

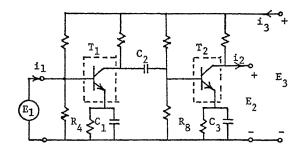

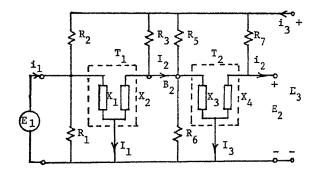

Fig. 3. The General Representation of the Voltage-Controlled Current Sources in a Multiple-Loop Feedback Amplifier.

Fig. 4. The Physical Interpretation of the Elements of the Return Difference Matrix with Respect to the Controlling Parameters of the Voltage-Controlled Current Sources.

6

# TECHNICAL BIOGRAPHY - D.A. MLYNSKI

Born 1932 in Berlin, Germany.

M.S. in 1958 from University Jena, Ph.D. in 1964 from Technical

University Aachen, Germany.

Industrial experience 1959 to 1964 at Siemens, R. & D. Lab.

Since 1964 academic positions.

Since 1973 Full Professor of EE at University Karlsmhe, Germany. Visiting Professor of EE 1969 and 1971 at University of Arizona, Tucson and in 1979 at University of California, Berkeley.

### D. A. Mlynski

# University Karlsruhe, F. R. Germany Visiting at University of California, Berkeley, Dept. EECS

# ABSTRACT

Existing layout concepts as used by electronic industry for LSI circuit layout are compared with the demands of VLSI circuit layout. The hierarchical layout approach is discussed and also the following new concepts: Maximal partitioning using cliques, multilayer planarization using Boolean equations, geometrical placement using a contour language and multilayer routability test using logical operations.

# INTRODUCTION

System designers are used to a top-down definition of different functional levels, e.g. key building blocks or subsystems, gates and basic circuit elements (Table 1).

|              | Functional Level | Layout Level |          |

|--------------|------------------|--------------|----------|

| top-<br>down | System           | Chip         | <b>+</b> |

|              |                  | Macro        | Bottom-  |

|              | Gate             | Cell         | up       |

|              | Circuit Element  | Device       |          |

# Table 1. Hierarchical Levels

However, since the early years of LSI the layout philosophy has been based rather on a bottom-up definition of layout levels. Moreover, on the cell level two gate array concepts are in use which do not provide macro levels (Table 2):

- (i) master slice concept(ii) standard cell concept

- (11) standard cell concept

| Cell Concept  | Cell Constraint                         | Array           |  |

|---------------|-----------------------------------------|-----------------|--|

| Master Slice  | Rectangles of uniform<br>size and shape | Matrix<br>array |  |

| Standard Cell | Rectangles of uniform<br>height         | Line<br>array   |  |

| General Cell  | Rectangular polygons                    | Arbitrary       |  |

Table 2. Cell Concepts for LSI and VLSI

The main advantage of these concepts is that the algorithmic difficulties of layout problems, especially of placement, are considerably reduced because of the more or less regular gate array. Efficient heuristic algorithms for placement (1-2) and for channel routing (3-5) are available and have been implemented in computer aided layout systems (6-7).

The main drawbacks are that channel-routing tends to long routing paths in parallel and, hence, to higher signal propagation times and signal crosstalk, and, still more important, that without availablility of macro levels the gate array approach hardly allows for a hierarchical layout. Obviously, these disadvantages become more serious with increasing scale of integration.

A third layout method in use is the general cell concept or custom design (Table 2). This provides a greater degree of freedom for shape and position of cells and position of pins on cell periphery. The advantages of this concept are more design flexibility, minimal chip area and, perhaps most important for VLSI, the availability of macros and hierarchical layout (8-9).

Hence, the general cell concept avoids the disadvantages of the more standardized gate array, however, on the expense that the algorithmic problems are much more complex and difficult. Many problems are still unsolved. So far, there is no working computer aided layout system based on this concept. Custom design method is in use only for manual design of LSI circuits on the device level for handling the necessarily less uniform devices and on the cell level if the single chip is produced in millions and consequently, design time does not dominate the overall production costs.

Nevertheless, it is a strong feeling of many in the field that making the general cell concept accessible to computer aided design it will be of optimal use to different design levels -- device, cell and macro level --, to different technologies and to both digital and analog circuits. Therefore it will be especially optimal for VLSI systems housing analog and digital circuits, random and regular logic and different technologies on a single chip.

# HIERARCHICAL LAYOUT APPROACH

A hierarchical layout approach consists of three main steps:

1) Partitioning.

The given system has to be partitioned hierarchically on a given number of levels. Usually, this will be based on a functional top-down definition of building blocks, gates etc., but also should be adequate to layout considerations by proper mapping between functional units and layout units.

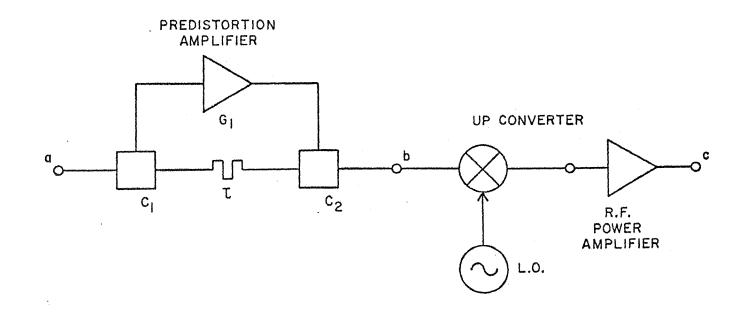

When partitioning has been done properly, the remaining two steps apply to each hierarchical level. In the following the functional terms circuit/component and the layout terms chip/cell, respectively, are used to represent any hierarchical level. 2) Topological layout.

The given circuit schematic diagram of components and interconnections is converted into a schematic layout or stick layout. This is only a first pass of approximate layout which provides a global chip planning by proper top-down algorithms. It does not take care of any geometrical constraints (e.g. dimensions of cells and wire routes) but only of topological constraints (global placement and wirability). Hence, the resulting schematic layout does not include accurate goemetrical dimensions and positions.

3) Geometrical layout

The schematic layout is converted into the actual layout. Only in this final pass all the geometrical requirements and design constraints are taken into account. Top-down or bottom-up placement algorithms or combinations of both may be used. Routing still may be split into two steps: Routability tests during the steps of placement improvement and actual routing after placement is finished.

Finally, it should be mentioned that interactive methods are necessary in all three parts of this approach at proper intermediate steps for the efficient handling of special technological designrules and unforeseen constraints.

The following sections give a discussion of some of the problems encountered in a hierarchical layout approach and possible solution methods and algorithms. They all are aimed to an implementation on a minicomputer with interactive graphics.

# PARTITIONING USING CLIQUES

Heuristic partitioning usually is done by bottom-up techniques of growing components from "seeds." For a good decision on the number  $\Gamma$  of seeds a knowledge of the upper bound  $\Gamma_{max}$  is

necessary. It can be found by maximum partitioning. However, this should not be based on devices but rather on the preceding top-down definition of functional units.

Each functional unit incident to n distinct interconnection nets is mapped into a complete graph on n nodes, i.e. into a clique (10). Hence, a graph representation of the given circuit is an aggregation of cliques. Clique aggregations have special properties which benefit the partitioning procedure. Especially, a clique is the only type of graph which does not posses an articulation set, i.e. cannot be partitioned.

The problem can be now restated as follows: Given a circuit with clique aggregation C. Find a minimum articulation set of C with maximum

The algorithm for maximal partitioning of graphs based on this clique concept is described in (10) and has been implemented on a DEC-computer PDP 11/60.

# MULTILAYER PLANARIZATION

A main problem of topological layout is to find a schematic layout with an approximate placement of cells that optimally benefits the routing.

Definition 1. Given an undirected bipartite graph G representing the given circuit. minimum set of branches B such that G-B is planar

is called a minimum planarizing set of G. The assignment of the elements of B to proper layers depends on technology. Different planarizations, i.e. different minimum planarizing sets, may cause different parasithic effects. Therefore, it is worthwhile to find the family  $\{B_v\}$  of all

minimum planarizing sets  $B_v$  in order to allow for an optimum choice.

In (11) a Boolean planarity function F has been introduced based on the following definition.

<u>Definition 2</u>. A binary variable  $u_{\lambda}^{J}$  is associated with branch j in layer  $\lambda$  such that:

$u_{\lambda}^{j} = \begin{cases} 0 & \text{if branch j is placed in layer } \lambda \\ 1 & \text{if branch j is NOT placed in layer } \lambda. \end{cases}$

A necessary and sufficient condition for planar multilayer layout of a circuit with planarity function F(u) of its associated circuit grah is (L = number of layers):

$$\sum_{\lambda=1}^{L-1} F(u_{\lambda}) + F(\prod_{\lambda=1}^{L-1} \overline{u}_{\lambda}) = 0,$$

where  $\pi$  denotes the Boolean AND and  $\Sigma$  the OR operator, as usually. The planarity function F(u)of the given circuit graph can be found by detection of wreathes (11).

For L = 2 the planarity equation reduces to:

$F(u) + F(\bar{u}) = 0.$

The set of solution vectors u corresponds to the family {B }. Each single solution vector  ${\bf u}$  represents a planar schematic layout which is found by planar embedding of G according to the values of the elements in the solution vector u. The method is well-adopted to computer implementation. Well-known minimization techniques of Boolean algebra can be used to optimize the solution.

# GEOMETRICAL PLACEMENT

The topological placement using multilayer planarization is a top-down technique. Hence, it seems appropriate to combine this with a bottomup geometrical placement. The procedure starts with a first cell and adds a single cell in each step of the procedure. Well-known constructive placement algorithms can be used for this step (12-13). However, they shall not be based on the circuit schematic diagram but rather on the schematic layout as represented by the planarized circuit graph.

Each single cell to be started with or to be added is a rectangular polygon of any complexity, i.e. of any number of rectangular corners. Consequently, the same holds for the resulting layout in all intermediate steps of the constructive placement.

Since the inner layout of cells is to be done in a different level of the hierarchic layout approach a description of layout contours is

sufficient on the cell level. This can be most efficiently done by a layout language using 12 different corner types (14). They differ from each other by two informations:

(i) in which direction a corner is approached and

(ii) change of direction from horizontal to vertical and vice versa at the corner.

(Supposed is a mathematical positive passage along the contour.) The complete description of a layout structure is given by an ordered corner sequence:

$\binom{\text{Cl}}{\text{Dl}} \binom{\text{C2}}{\text{D2}} \binom{\text{C3}}{\text{D3}} \cdots \cdots \binom{\text{Cn}}{\text{Dn}}$ ,

where Ci is the type of corner i and Di its distance to the next corner in order.

Integer numbers can be associated with the corner types. Then, basic layout operations, e.g. rotations by multiples of 90° and flipping of layout structures, can be done efficient by INTEGER operations.

#### MULTILAYER ROUTABILITY TEST

Routability has to be tested at proper steps of the hierarchical layout procedure based on the approximate or final placement of cells. The problem can be stated as follows: Given an order of nets and layout structures in the different layers (cells and routing paths). Test whether the next net is routable and find layer assignment and vias.

A strict automatic multilayer routability test (15) has been based on a set theoretic description and processing of the given layout structures in all layers. The following two concepts are essential:

(i) Domain is the union of all points in a single layer, which are planar routable within this layer.

(ii) Two domains in adjacent layers are called incident if their intersection is not empty.

Technologically the incidence of two domains opens the possibility of a via between adjacent layers. Since the basic concept is free of any metric it is independent of technology. It can be adjusted to any technology by implementing metric constraints.

The routability test is based on the following:

<u>Theorem</u>. A net with m pins is routable on n layers if and only if the following holds: An ordered sequence of domains  $(A, B, C, \ldots, Z)$  exists for each pin pair  $\{a, z\}$  in a set of (m-1)independent pairs of pins of the net such, that  $a \in A$  and  $z \in Z$  and adjacent domains in the sequence are incident.

The routability test is described in (15). It only needs logical operations and is independent of the choice of a starting pin.

#### ACKNOWLEDGEMENT

Research sponsored by the National Science Foundation Grant ENG78-24425.

#### REFERENCES

- M. Hanan, P. K. Wolff, B. J. Agule, "A Study of Placement Techniques," J. Design Antom. & Fault-Tolerant Comp. Vol. 1, 1976, p. 28-61.

- (2) M. A. Breuer, "Min-cut Placement," J. Design Autom. & Fault-Tolerant Comp. Vol. 1, 1977, pp. 343-362.

- (3) B. W. Kernighan, D. G. Schweikert, G. Persky, "An optimum Channel-Routing Algorithm for Polycell Layouts of Integrated Circuits," Proc. 10th Design Autom. Workshop 1973, pp. 50-59.

- (4) D. N. Deutsch, "A Dogleg Channel Router," 13th Design Autom. Conf. San Francisco 1976, pp. 425-433.

- (5) N. Nan, M. Feuer, "A Method for the Automatic Wiring of LSI Chips," Proc. AFIPS, 1978, pp. 297-302.

- (6) K. Koller, W. Kubosch, U. Lauther, "Computer-Aided Design of MOS-LSI Circuits Using the AVESTA Program System," Siemens FEB Vol. 5, 1976, pp. 350-352.

- (7) G. Persky, D. N. Deutsch, D. G. Schweikert, "LTX -- A Minicomputer Based System for Automated LSI Layout," J. Design Autom. & Fault-Tolerant Comp. Vol. 1, 1977, pp. 217-256.

- (8) B. T. Preas, C. W. Gwyn, "Methods for Hierarchical Automatic Layout of Custom LSI Circuit Masks," Proc. 15th Design Autom. Conf. Las Vegas 1978, pp. 206-212.

- (9) W. R. Heller, "Wirability Study for Custom Chips," 1978, private communication.

- (10) A. E. Engel, D. A. Mlynski, "Maximal Partitioning of Graphs," Proc. ISCAS Tokyo, 1979.

- (11) T. Dorn, D. A. Mlynski, "Multilayer Layout Planarization Using Boolean Algebra," Proc. ISCAS Tokyo, 1979.

(12) J. M. Kurtzberg, "Backboard Wiring Algorithms

- (12) J. M. Kurtzberg, "Backboard Wiring Algorithms for the Placement and Connection Order Problems," Burroughs Report TR60-40, 1960.

- J. M. Kurtzberg, "Algorithms for Backplane Formation," in Microelectronics in Large Systems, Spartan Books 1965, pp. 51-76.

- Systems, Spartan Books 1965, pp. 51-76.

K. D. Brinkmann, "Layout Description by Means of Corner Types," Proc. ISCAS Toryo, 1979.

- (15) M. Wiesel, D. A. Mlynski, "Verdrahtungs-Algorithmus fucr Mehrebenenentwurf bei hoher Packungsdichte," Proc. IEEE/NTG-Fachtagung Hoechstintegrierte Schaltungen, Baden-Baden 1979.

4

# FUZZY TENSIONS AND POTENTIALS IN QUALITATIVE ANALYSIS OF NETWORK PROBLEMS

Kenji Onaga

Wataru Mayeda

Department of Circuits and Systems Faculty of Engineering

Division of Information Sciences Faculty of Integrated Science and Arts

Hiroshima University Senda-cho, Hiroshima, Japan

#### ABSTRACT

A new concept of fuzzy tension and fuzzy potential is proposed as a mathematical tool for qualitative analysis of network problems. In this paper we first describe modeling of curriculum networks and fail-safe networks in which the concept of fuzzy tension appears naturally as an well-balanced curriculum plan or reliability assignment. Algebraic properties of fuzzy tensions and potentials are thoroughly investigated and consistency of specifications is shown to be expressible by a simple condition on circuits.

MODELING OF CURRICULUM AND FAIL-SAFE NETWORKS

#### 1. Curriculum Networks

A curriculum of an educational institute or program is an interconnection of course works and can be modeled by a weighted directed graph G=(V, E) of the node set V and edge set E. A node x represents a state of education and an edge e=(x,y) represents a course work whose teaching starts from state x and ends at state y. Course e possesses educational contents: maximum goal  $\beta(e)$  and minimum requirement  $\alpha(e)$ .  $\alpha$  or  $\beta$ is a list of teaching items to be covered by the teacher and associated grades of the student's knowledge level. An actual scholastic achievement t(e) gained from course work e lies somewhere inbetween  $\alpha(e) \leq t(e) \leq \beta(e)$ .

Here we express  $\alpha$  (or  $\beta$ , t) by a vector

$\alpha(e) = (\alpha_1(e), \alpha_2(e), ..., \alpha_L(e))$ where component value  $\alpha_i(e)$  represents the grade of knowledge level or scholastic gain on teaching item #i from course work e. The component valuemay be 1 or 0 if knowledge level or scholastic gain is yes or no type nature, but often assumes a real number in [0,1]. Note that these quantities are regarded as fuzzy sets.

We assume the following notations and conventions. iff  $\alpha_i \leq \beta_i$  for all i **(1)**α **≤** β

(2)  $\alpha \vee \beta = \gamma$ ,  $\gamma i = \max(\alpha_i, \beta_i)$ (3)  $\alpha \wedge \beta = \gamma$ ,  $\gamma_i = \min(\alpha_i, \beta_i)$ (4)  $\alpha \sim \beta = \gamma$ ,  $\gamma_i = \{\alpha_i \text{ if } \alpha_i > \beta_i\}$ 6 otherwise

(5)  $\Theta = (0, 0, \dots, 0), I = (1, 1, \dots, 1).$

When the component value is 1 or 0 type,  $\alpha(\text{or }\beta)$ , t) is just the characteristic value representation of a subset of a finite teaching item set U= {#1,#2,..., #L} and the above notations are reduced to the ordinary set theoretic notations, c, U, A, -.

Anode x represents a state of knowledge level at node x of the curriculum network  $N=(G, \alpha, \beta)$  where graph G represents a precedence relation among course works. A quantitative measure of the student's knowledge level at node x is denoted by a fuzzy set

- $\pi(x).$   $\pi$  and t are assumed to obey the following rule. (a) For each edge e=(x,y) in E

- $\alpha(e) \leq t(e) \leq \beta(e), \pi(y) = \pi(x) \vee t(e),$

- (b) If two edges a=(x,z) and b=(y,z) are incident to node z, we require a balancing condition  $\pi(x) \vee t(a) = \pi(y) \vee t(b)$ to hold.

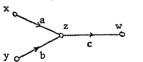

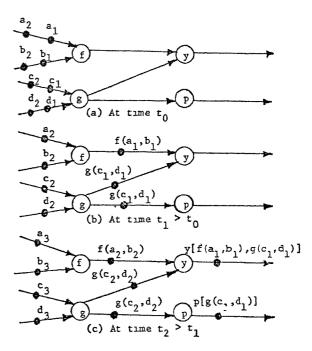

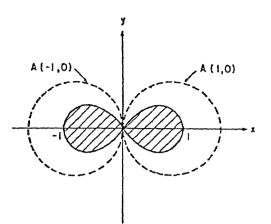

Reasons behind these rules are as follows (no generality is lost even if discussion is made on a single teaching item, say #i): Rule (a) expresses nature of learning. Understanding of #1 is hierarchical so that gain  $t_1(e)=0.5$  does not contribute to an increase in knowledge if the initial knowledge level is already higher, say  $\pi_i(x)=0.6$ , but does contribute when the initial level is lower, say  $\pi_i(x)=0.4$ . Hence our assumption is that learning takes place only when the gain exceeds the initial level. Rule (b) expresses balanced teaching of well-coordinated curriculum. Suppose unbalance  $\pi(x) \vee t(a) \neq \pi(y) \vee t(b)$  has taken place in Fig.1

Fig.1 Explanation of rule (b), the balancing condition at node z.

For course work c=(z,w), the teacher must base his teaching on students' common knowledge level at node z. Some students take a.c combination with  $\pi(x)Vt(a)$ and others b.c combination with  $\pi(y)Vt(b)$ . Hence  $\pi(z) = [\pi(x)Vt(a)] \wedge [\pi(y)Vt(b)].$

This unbalance may be viewed as loss and can be avoided by good coordination among courses by imposition of rule (b).

Good coordination is expressed more rigorously by Kirchhoff's voltage law on fuzzy sets,

FKVL:  $V_{e \in L^{\dagger}} t(e) = V_{e \in \overline{L}} t(e)$ for all circuits  $L = L^{\dagger} v \overline{L}$  where  $L^{\dagger}$  (or  $\overline{L}$ ) is the set of forward (or backward) edges whose edge direction agrees (or disagrees) with the circuit orientation. Scholastic gain t satisfying FKVL is called a fuzzy tension on the curriculum network N. It is quite natural to expect some progress from any course work, hence

Monotonicity:  $\pi(x) \leq \pi(y)$ holds for all e=(x,y) in E. In general a mapping from the node set V into fuzzy set is called a fuzzy potential of G if it satisfies the monotonicity. A curriculum is a fuzzy tension satisfying Admissibility:  $\alpha(e) \leq t(e) \leq \beta(e)$

for all edges in E.

- Problems immediately confronting us are

- . feasibility condition of existence of admissible tensions in N (consistency of requirement  $\alpha(e)$ and goal  $\beta(e)$ .

- construction of an admissible tensiont in N.

- maximum scholastic achievement of the program.

In this paper we will present answers to these questions by means of thorough investigation of algebraic properties of fuzzy tensions and potentials.

# 2. Fail-Safe Networks

Functional interconnection of a system is conveniently expressed by a directed graph G=(V,E) where a node represents a subsystem and an edge represents a functional connection between associated nodes. To each edge e=(x,y) there is a weight  $\beta(e)$  which is a list of failure susceptibility  $\beta_i(e)$  (not necessarily probability) of node x affecting node y with regard to failure cause #i in the failure cause set U= {#1,  $\#2,\ldots,\#F\}.$  Larger value  $\beta_{\tt i}(e)$  more susceptible to failure cause #i.

If two edges a=(x,y) and b=(y,z) are in tandem, the failure cause accumulates and a higher susceptibility dominates a lower one for the same cause. Hence letting  $\pi(x)$  denote the failure potential at node x, we have

$\pi(\mathbb{Z}) = \pi(\mathbf{x}) \vee \beta(\mathbf{a}) \vee \beta(\mathbf{b}).$

In the network, incidence of two edges a=(x,z) and b=(y,z) into node z means a fail-safe mechanizm operating at z such that, for failure cause #i, the mechanism chooses the smaller susceptibility for  $\pi(z)$  $\pi(z) = [\pi(x) \vee \beta(a)] \wedge [\pi(y) \vee \beta(b)].$

In designing a fail-safe network, we have some control over distribution of available resources to realizing failure susceptibility of each interconnection. Realized susceptibility of interconnection e, t(e), is bounded above by the network specification  $\beta(e)$  and below by technology  $\alpha(e)$ . Therefore susceptibility assignment t satisfies the admissibility  $\alpha(e) \leq t(e) \leq \beta(e)$  on each e in E. Since unbalanced assignment is waste of resources, we should require the balancing condition  $\pi(x) \vee t(a) = \pi(y) \vee t(b)$ .

We proceed as before in the case of the curriculum network and conclude that well-balanced reliability assignment may be adequately modeled by an admissible fuzzy tension in the fail-safe network  $N=(G, \alpha, \beta)$ .

# DEFINITIONS OF FUZZY TENSIONS AND POTENTIALS