# Interconnected alternating-current light-emitting diode arrays isolated by laser micromachining

Giuseppe Y. Mak, Edmund Y. Lam, and H. W. Choi<sup>a)</sup>

Department of Electrical and Electronic Engineering, The University of Hong Kong, Pokfulam Road, Hong Kong, China

(Received 27 September 2010; accepted 11 December 2010; published 11 January 2011)

The fabrication and operation of a monolithic InGaN alternating-current light-emitting diode (LED) based on the bridge rectifier design are demonstrated. The device consists of on-chip interconnected LED elements that have been isolated by direct-write laser micromachining, a powerful tool well-suited for rapid device prototyping. The effects of capacitors coupled to the dc path of the rectifier have been investigated. Although an increase of radiant flux can be achieved through capacitive voltage smoothening, the wall-plug efficiency drops as a result. The device can be applied to  $12~V_{rms}$  lighting applications. © 2011 American Vacuum Society. [DOI: 10.1116/1.3533949]

## I. INTRODUCTION

The notion of energy savings has driven a quest for more efficient light sources in the lighting industry. In the past decade, compact fluorescent lamps (CFLs) have gradually become a substitute for incandescent light bulbs. However, the presence of mercury in CFLs has raised concerns regarding their disposal.<sup>2</sup> As a promising candidate to replace CFLs, light-emitting diodes (LEDs) possess the advantages of higher efficiency, longer lifetime, faster switching, and absence of toxic substances. However, before the widespread adoption of LEDs in general lighting becomes a reality, several issues remain to be addressed, one of which being the type of the input voltage. Physically, LEDs are inherently p-n junctions and thus require direct current (dc) to operate. Until future-generation renewable power sources such as wind turbines and solar cells that generate dc voltages become prevalent, most power stations worldwide currently only supply alternating-current (ac) voltage. When LEDs operate directly under ac voltage, they will only light up during less than half of the operation time. Therefore, external rectifiers and regulators (integrated as LED drivers<sup>3-6</sup>) are usually installed to provide the required regulated dc voltage. This arrangement inevitably leads to increased heat loss, bulky design, and shortened lifetime (due to the short lifetimes of electrolytic capacitors commonly used in LED drivers) of LED luminaires.

To solve this problem, there is an increasing interest toward "driverless" LED chips (known as ac-LED thereafter) which can be directly coupled to ac voltage sources, considering that LEDs are in fact diodes. The antiparallel design was an early solution to this problem, whereby two series of on-chip LEDs were connected in parallel but conducted in opposite directions. In each half-cycle of the sinusoidal ac voltage, half of the LEDs light up. To increase the proportion of LEDs that radiate in each half-cycle, we adopt the full-wave bridge rectifier design in the present work. In this design, a portion of the on-chip LEDs function as the full-wave

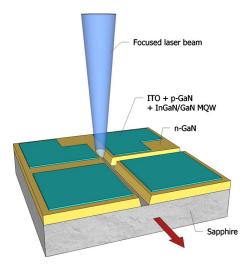

The layout of typical ac-LED chip involves multiple isolated LED elements interconnected via metallic interconnects. Isolation requires complete removal of semiconductor material between devices; for nitride LED wafers up to 4  $\mu m$  of GaN must be removed. Traditionally this step is carried out with dry etching through a masking layer. Either a thick masking layer or a material with high etch selectivity to GaN is needed for that purpose. In this work an alternative process has been adopted for device isolation between individual LED elements. Instead of performing plasma deep etching, deep trenches are formed by direct-write laser micromachining—a maskless and high-speed process particularly suitable for rapid device prototyping (Fig. 1). This eliminates the need for lithographic processes and also considerations for etch selectivities and rates for deep etching. Complete design, fabrication, and operating characteristics of our proposed chip are discussed in the following sections.

#### II. EXPERIMENTAL DETAILS

## A. Circuit design

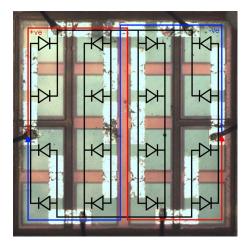

Our ac-LED chip is designed to operate under 12  $V_{rms}$  sinusoidal ac voltage, consisting of 16 identical individual LED elements whose dimensions are each  $250\times250~\mu m^2$ . Figure 2 shows a microphotograph of the entire chip, together with the circuit diagram superimposed on top. The rectifier is formed by four groups of LEDs at the corners of the chip, each of which consists of two LEDs connected in parallel. The remaining eight LEDs connected in parallel in the center of the chip constitute the devices along the dc path. During the positive half-cycle of the ac voltage, the current flows in the direction illustrated by the red arrow (marked as +ve), whereas during the negative half-cycle, it flows in the direction of the blue arrow (marked as -ve). As a result, the current flows through the dc path in both half-

rectifier, whereas the other LEDs (known as dc-path LEDs) receive dc voltage from the rectifier. Although the rectifier LEDs still radiate during half a cycle only, the dc-path LEDs can radiate during both half-cycles, thus maximizing the light output.

<sup>&</sup>lt;sup>a)</sup>Electronic mail: hwchoi@hku.hk

Fig. 1. (Color online) Trench formation by direct-write laser micromachining process. As the chip is translated in the direction of the red arrow, the stationary laser beam ablates the n-GaN layer while leaving the underlying sapphire layer intact.

cycles, and more LEDs are connected along the dc path to maximize the chip area that radiates in each period. During each half-cycle, effectively three groups of LEDs conduct, i.e., two groups of rectifier LEDs and one group of dc-path LEDs. Since the typical forward voltage of GaN-based LED lies in the range of 2.8–4 V, the total voltage drop sums to about 9–12 V, matching well the design supply voltage.

## **B.** Fabrication process

The ac-LED chip was fabricated on an InGaN/GaN blue-light LED wafer ( $\lambda_{emission}$ =470 nm) with indium tin oxide coating ( $\sim$ 200 nm) as the current spreading layer. The active regions were patterned by standard photolithography, followed by dry etching to expose the *n*-GaN regions. Individual micro-LED elements were completely isolated from

Fig. 2. (Color online) Microphotograph showing layout of ac-LED, with circuit diagram superimposed. The directions of current flow during the positive and negative cycles of a sinusoidal voltage are shown with the red arrow (marked as "+ve") and the blue arrow (marked as "-ve"), respectively. The overall dimensions of the device array are 1.38×1.38 mm<sup>2</sup>.

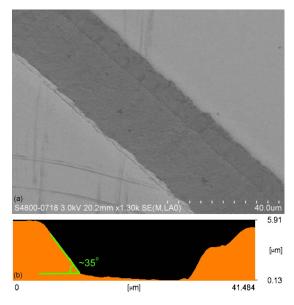

Fig. 3. (Color online) (a) field-emission scanning electron microscopy (FE-SEM) image of a GaN trench formed by UV laser micromachining in air. The focus offset (above the best focal plane), pulse energy, pulse repetition rate, and scan speed were 450  $\mu$ m, 23  $\mu$ J, 5 kHz, and 25  $\mu$ m/s, respectively. Only single pass of scan was required to produce the trench. (b) Atomic force microscopy cross-section of the trench.

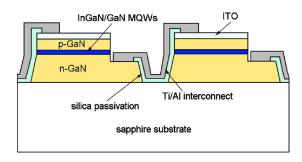

each other for proper operation by laser micromachining. The collimated Gaussian beam from an ultraviolet (UV) diode-pumped solid-state laser ( $\lambda = 349$  nm, full width at half maximum pulse duration=4 ns) was focused by an UV objective lens of focal length equal to 19 mm to a tiny spot onto the sample. The sample was placed onto an  $x-y-\theta$  motorized stage, where the translational and rotational motions were computer-controlled and monitored by a chargecoupled device (CCD) camera confocal to the optics. The laser process produced flat-bottom trenches 20-30 µm in width and  $3-4 \mu m$  in depth that terminated abruptly at the GaN-sapphire interface as a result of the dissimilar ablation thresholds between GaN and sapphire, as illustrated in Fig. 3(a). The trenches also had inclined sidewalls [sidewall angle of  $\sim 35^{\circ}$ , as shown in Fig. 3(b)] which were beneficial for the subsequent deposition of isolation oxide and metallic interconnects. Subsequently, a SiO<sub>2</sub> layer (100 nm) for isolation was deposited by electron beam evaporation. Photolithographic patterning and Ar/CHF<sub>3</sub> dry etch were then carried out to expose the p-contact and n-contact regions. To connect the isolated LED elements, Ti/Al (40 nm/300 nm) interconnects were deposited by a liftoff process. This metal layer was annealed in N<sub>2</sub> ambient at 600 °C for 30 s in order to reduce the contact resistance. The ac-LED die was then packaged onto a TO-header for testing and evaluation. The schematic diagram in Fig. 4 offers a cross-sectional view of the device structure.

## III. RESULTS AND DISCUSSION

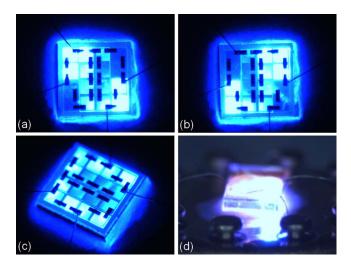

The ac-LED device was tested by applying a sinusoidal ac voltage of 12  $V_{rms}$  (i.e., amplitude=16.97 V) across the input terminals. As illustrated in Figs. 5(a) and 5(b), while the

Fig. 4. (Color online) Cross-sectional schematic diagram of an ac-LED. The two on-chip LEDs shown in the diagram are isolated by laser-micromachined trenches. They are then connected by Ti/Al interconnect. The inclined sidewalls of the trenches are passivated by SiO<sub>2</sub>.

rectifier LEDs on the left and right sides of the chip radiated alternately during the positive and negative half-cycles, the dc-path LEDs radiated in both half-cycles, albeit at lower intensities due to resistive matching. The combined effect is shown in Fig. 5(c), where the frequency of ac voltage was adjusted so that the CCD camera was able to capture light emission from both half-cycles. The suitability of the ac-LED for lighting is demonstrated by coating the chip with a mixture of CdSe/ZnS core-shell quantum dots with emission wavelengths at 564 and 610 nm; Fig. 5(d) shows the operation of this white light ac-LED.

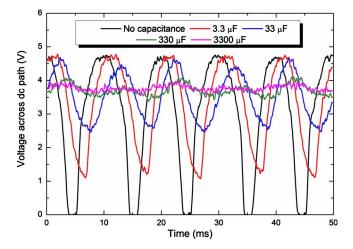

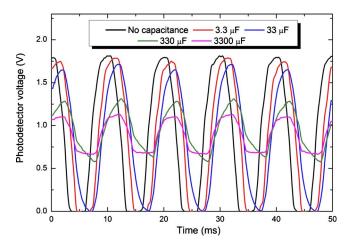

A capacitor can be added across the dc path to smoothen the ripples of the rectified dc voltage. <sup>10</sup> Its effect toward the dc-path voltage, radiant flux, and wall plug efficiency (WPE, defined as the radiant flux divided by the average input power; the average input power was found by numerically integrating the product of instantaneous current and voltage over a period and dividing the result by the time of a period) was determined. Electrolytic capacitors of different capacitances were coupled to the dc path when an input voltage of  $12~V_{rms}$  at 50~Hz was applied to the chip. The time-varying dc-path voltage was measured real-time with a digital oscilloscope. Concurrently, an optical fiber of  $400~\mu m$  diameter

Fig. 5. (Color online) Microphotographs of ac-LED operating under a sinusoidal ac voltage of 12  $\,{

m V}_{rms}$ : (a) positive half-cycle; (b) negative half-cycle; (c) full cycle; (d) quantum-dot-coated ac-LED with white light emission.

Fig. 6. (Color online) Variation of voltage across the dc path under different capacitances.

was placed about 1 mm above the chip, and the collected light was coupled to a high-speed Si photodetector (Thorlabs SV2-FC) to measure the time-varying optical output. The results are plotted in Figs. 6 and 7, respectively. Referring to the black curves in both figures, in the absence of capacitance, the dc-path voltage oscillated at a frequency of 100 Hz between 0 and 4.8 V. The dc-path LEDs are switched on and off repeatedly at this frequency, reflected in the variation of the photodetector voltage. When electrolytic capacitors are coupled to the dc path, the charging and discharging of the capacitors help to decrease the voltage variations along the dc path. As observed in Fig. 6, the voltage ripple amplitude decreases from  $\sim 3.8 \text{ V}$  for  $3.3 \mu\text{F}$  to  $\sim 0.2 \text{ V}$  for 3300  $\mu$ F. With capacitors of 330  $\mu$ F or above, the dc-path voltage stays within 3.5–4 V. Based on the *I-V* characteristics of the dc-path LEDs (not shown), this is the voltage range for which the forward current is about 20 mA. The dc-path LEDs can thus be turned on constantly. The magenta and green curves in Fig. 7 highlight this point. At the minima of these two curves, the photodetector voltage never drops to zero. Instead it drops to  $\sim 0.7$  V ( $\sim 61.4\%$  of the photode-

Fig. 7. (Color online) Light output variation as a result of the addition of capacitance.

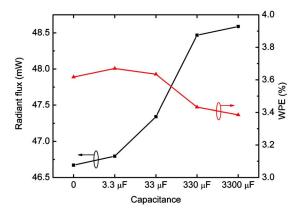

Fig. 8. (Color online) Plots of radiant flux and WPE with increasing capacitance.

tector peak voltage for 3300  $\mu$ F) before rising up again. The dc-path LEDs are still radiating at these instances, contributing to an increase in radiant flux.

As shown in Fig. 8, the radiant flux rises with increasing capacitance value (curve with square markers). The radiant flux increases by 4.3% when a 3300  $\mu$ F capacitor is used. Nevertheless, this improvement comes at a cost. Shown in the same figure is the trend of WPE, which decreases with increasing capacitances. When the capacitance increases from 0 to 3300  $\mu$ F, the WPE drops from 3.62% to 3.39%. This drop can be attributed to the presence of the equivalent series resistance ( $R_{ESR}$ ) and the increased charging and discharging current drawn by the large capacitors  $(I_C)$ . As the power dissipated by a capacitor is approximately given by  $I_{\rm C}^2 R_{\rm ESR}$ , assuming  $R_{\rm ESR}$  to be constant, the increase in  $I_{\rm C}$  can lead to an increase in heat dissipation and hence a drop in WPE.

The need for capacitance in an ac-LED is arguable. Although capacitors can reduce the fluctuation of dc-path voltage and light intensity variation, the human eyes will in fact not be able to notice any flickering when the frequency of variation is as high as 100 Hz. On the other hand, although the radiant flux increases due to capacitance, the WPE drops due to  $R_{\rm ESR}$ . This drop in WPE may be aggravated when aging of capacitors results in further increase in  $R_{\rm ESR}$ . Therefore, if the design goal is to maximize the WPE, capacitors should not be included. Nevertheless, if radiant flux maximization and stabilization are required, capacitors will be needed. In addition, capacitors with smaller  $R_{\rm ESR}$ , longer lifetimes, and smaller sizes (such as surface-mount solid tantalum capacitors) should be used in lieu of bulky and shortlived electrolytic capacitors.

Another issue of ac-operation is the effects of reverse bias stress on the diodes. In the present design, the peak reverse voltage encountered by each LED in the rectifier is about 11 V. At this voltage level, the reverse current is only of the order of 0.1 µA. Since GaN-based LEDs do not show appreciable degradation below reverse stress current of 0.5 mA, 11,12 the lifetimes of the rectifier LEDs should not be significantly affected.

#### IV. CONCLUSION

We have demonstrated the fabrication and operation of a GaN-based bridge-type ac-LED chip targeted at 12  $\,\mathrm{V}_{\mathrm{rms}}$  applications. The fabrication process involved direct-write laser micromachining of deep trenches on GaN material for device isolation, replacing conventional lithographic and deep dry etch processes. We have also studied the effect of a capacitor coupled in parallel with the dc path. It is found that the radiant flux of ac-LED increases with the capacitance, while the WPE shows the opposite trend. By balancing the advantages and disadvantages offered by capacitors, we conclude that capacitors are beneficial for ac-LED in terms of the increase in radiant flux (4.3% in our experiments). The influence on WPE can be reduced by using capacitors of small equivalent series resistance (ESR), long lifetime, and small size.

#### **ACKNOWLEDGMENT**

This work was supported by a GRF grant of the Research Grant Council of Hong Kong (Project No. HKU 7118/09E).

<sup>1</sup>M. H. Crawford, IEEE J. Sel. Top. Quantum Electron. 15, 1028 (2009). <sup>2</sup>N. C. Johnson, S. Manchester, L. Sarin, Y. M. Gao, I. Kulaots, and R. H. Hurt, Environ. Sci. Technol. 42, 5772 (2008).

<sup>3</sup>G. Carraro, *Proceedings of IEEE Conference on APEC* (Institute of Electrical and Electronics Engineers, New York, 2007), pp. 1316-1318.

W. Chang, D. Chen, H. Nien, and C. Chen, Proceedings of IEEE Conference on APEC (Institute of Electrical and Electronics Engineers, New York, 2008), pp. 558-564.

<sup>5</sup>Y. Hu and M. M. Jovanović, IEEE Trans. Power Electron. 23, 3116 (2008).

<sup>6</sup>B. Wang, X. Ruan, K. Yao, and M. Xu, IEEE Trans. Power Electron. 25, 592 (2010)

<sup>7</sup>J.-P. Ao, H. Sato, T. Mizobuchi, K. Morioka, S. Kawano, Y. Muramoto, Y.-B. Lee, D. Sato, Y. Ohno, and S. Sakai, Phys. Status Solidi A 194, 376 (2002).

<sup>8</sup>G. Y. Mak, E. Y. Lam, and H. W. Choi, J. Vac. Sci. Technol. B 28, 380 (2010).

<sup>9</sup>H. W. Choi, C. W. Jeon, and M. D. Dawson, J. Vac. Sci. Technol. B 23, 99 (2005).

<sup>10</sup>A. S. Sedra and K. C. Smith, Microelectronic Circuits (Oxford University Press, New York, 1998), Vol. 4, Chap. 3, p. 185.

<sup>11</sup>M. Meneghini, U. Zehnder, B. Hahn, G. Meneghesso, and E. Zanoni, IEEE Electron Device Lett. 30, 1051 (2009).

<sup>12</sup>N. C. Chen, Y. N. Wang, Y. S. Wang, W. C. Lien, and Y. C. Chen, J.

Cryst. Growth 311, 994 (2009).