# Tapered sidewall dry etching process for GaN and its applications in device fabrication

H. W. Choi, C. W. Jeon, and M. D. Dawson

Citation: J. Vac. Sci. Technol. B 23, 99 (2005); doi: 10.1116/1.1839914

View online: http://dx.doi.org/10.1116/1.1839914

View Table of Contents: http://avspublications.org/resource/1/JVTBD9/v23/i1

Published by the AVS: Science & Technology of Materials, Interfaces, and Processing

## **Related Articles**

Characteristics of silicon etching by silicon chloride ions

J. Vac. Sci. Technol. A 31, 031301 (2013)

Surface properties of c-plane GaN grown by plasma-assisted molecular beam epitaxy

J. Vac. Sci. Technol. B 31, 03C112 (2013)

Controlling the silicon nanowire tapering angle in dense arrays of silicon nanowires using deep reactive ion etching

J. Vac. Sci. Technol. B 31, 021806 (2013)

Chamber conditioning process development for improved inductively coupled plasma reactive ion etching of GaAs/AlGaAs materials

J. Vac. Sci. Technol. B 31, 021207 (2013)

Wet etching silicon nanofins with (111)-oriented sidewalls

J. Vac. Sci. Technol. B 31, 021801 (2013)

## Additional information on J. Vac. Sci. Technol. B

Journal Homepage: http://avspublications.org/jvstb

Journal Information: http://avspublications.org/jvstb/about/about\_the\_journal Top downloads: http://avspublications.org/jvstb/top\_20\_most\_downloaded

Information for Authors: http://avspublications.org/jvstb/authors/information\_for\_contributors

## **ADVERTISEMENT**

## Tapered sidewall dry etching process for GaN and its applications in device fabrication

H. W. Choi, a) C. W. Jeon, and M. D. Dawson

Institute of Photonics, University of Strathclyde, Wolfson Centre, 106 Rottenrow, Glasgow G4 0NW, United Kingdom

(Received 29 June 2004; accepted 1 November 2004; published 5 January 2005)

A method of etching which allows the direct interconnection of multiple GaN-based devices is introduced. The mesa structures of devices are etched using an isotropic recipe which produces tapered sidewalls. The degree of inclination can be readily controlled through various etching parameters, which include the inductively coupled plasma power, plate power, and pressure, thus modifying the vertical and lateral etch components. This approach has been successfully adopted in the fabrication of interconnected and matrix-addressable microlight-emitting diodes, and offers superior optical and electrical performance and a high degree of uniformity compared to similar devices fabricated using conventional processes. © 2005 American Vacuum Society.

[DOI: 10.1116/1.1839914]

#### I. INTRODUCTION

The formation of mesa structures in the fabrication of GaN-based photonic devices is commonly achieved through dry etching processes, due to the resistance of the material to wet chemical etching. Of these, inductively coupled plasma (ICP) dry etching has proven to be particularly attractive, offering etch rates of up to  $\sim 1~\mu m$  per minute compared to tens of nanometers per minute for conventional reactively ion etching (RIE). Typically, the etch process should yield high etch rates and selectivities, minimal surface roughening, good reproducibility, and a high degree of anisotropy. All of these properties can be achieved with ICP etching.

Anisotropic etching produces vertical and smooth sidewalls, which is critical for the operation of the edge-emission laser. However, other photonic devices like light-emitting diodes (LEDs) and vertical cavity surface emitting lasers (VCSELs) do not strictly require vertical sidewalls. While nonvertical sidewalls may not make a significant difference to a single device, they can play an important role in the interconnection of multiple devices in an array.

Arrays of microsized LEDs and VCSELs have been demonstrated in recent years, <sup>2,3</sup> as devices which can be used as microdisplays and optical switches in communication networks. Interconnection of individual devices cannot be achieved through direct metal lines, since the metal layer cannot provide satisfactory step-coverage across the sharpedged mesa structure.

Traditionally, the problem has been overcome by the process of planarization. A sacrificial material is deposited over a surface with uneven topology. This is followed by planarization through dry etching or chemical-mechanical polishing to expose the device regions. While planarization has been adopted for the fabrication of GaN-based devices, it is not without drawbacks. Nonrecoverable damage often forms on the *p*-type GaN surface due to etching or abrasion. <sup>5,6</sup> This

manifests itself in the form of degraded electrical and optical properties in the fabricated devices. More importantly, nonuniformity in light emission across the array is often observed.

Consequently, the tapered-sidewall approach is introduced in this article to target this problem. The sidewalls of the individual devices can be made to have an inclination of  $20^{\circ}-45^{\circ}$  to the vertical. As a result, conformal step coverage is possible for mesa structures with a height of up to  $\sim 5~\mu m$ . Not only can devices can be interconnected directly by metal lines with this process, but improvements to the planarization scheme can also be achieved, as void formation can be avoided during deposition of the sacrificial material (such as  $SiO_2$ ).

#### II. EXPERIMENTAL DETAILS

The tapered sidewalls were formed by ICP etching using a STS Multiplex ICP system. ICP etching is suitable because of its ability to control the vertical and lateral etch components through the variation of parameters, which include the ICP and plate powers, ambient pressure and temperature, and the gas chemistries. Mesa structures with widths of 20  $\mu m$  and a separation of 4  $\mu m$  were etched using photoresist as a masking material (Shipley SPR220, nominal thickness of 7  $\mu m$ ) under a range of conditions. The sidewalls were analyzed by cleaving the samples across the mesa structures and the cross-sectional profile was examined by scanning electron microscopy.

#### III. RESULTS AND DISCUSSIONS

#### A. Tapered-sidewall etching

A variety of process recipes can be tailored to meet the specifications, depending on their specific purposes. In this study, the plasma chemistry for the processes were fixed at 20 sccm  $\text{Cl}_2/8$  sccm  $\text{BCl}_3/5$  sccm Ar, while the temperature and pressure were maintained at 30 °C and 5 mTorr, respectively. On the other hand, the ICP and plate powers

<sup>&</sup>lt;sup>a)</sup>Electronic mail: anthony.choi@strath.ac.uk

TABLE I. Typical conditions for anisotropic etching of GaN.

| Conditions | ICP<br>power/W | RIE<br>power/W | dc<br>bias/V | Etch rate/<br>nm min <sup>-1</sup> | Selectivity | Inclination (°) |

|------------|----------------|----------------|--------------|------------------------------------|-------------|-----------------|

| A          | 550            | 65             | -160         | 2240                               | 1:1.3       | ~25             |

| В          | 650            | 50             | -125         | 1670                               | 1:2.13      | ~33             |

| С          | 650            | 30             | -90          | 767                                | 1:2.96      | ~40             |

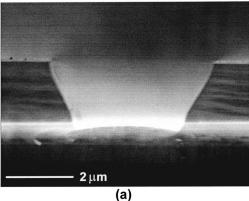

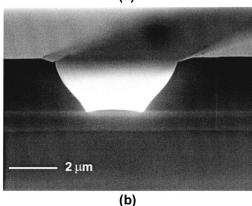

were varied to produce direct current (dc) bias ranging from −90 to −160 V. The complete list of processing conditions is tabulated in Table I. It can be seen that as the dc bias is reduced, the gradient of the tapered sidewall also reduces. This can be understood in terms of the directionality of the ions in the plasma. To achieve an anisotropic etch, a large RIE platen power is typically applied resulting in impinging ions having high energies and acceleration in the vertical direction. When the dc bias voltage is reduced, ion energies are lower and influence from the vertical electric field is reduced. This effect is enhanced by the lateral force component introduced by the ICP power coil around the chamber. Hence, ions are not confined to vertical pathways. Under such conditions, areas close to the edge of the masking material are less likely to be exposed to the ions, and a tapered sidewall is produced. Cross-sectional scanning electron microscopy (SEM) images of mesa structures etched under conditions A and C are shown in Figs. 1(a) and 1(b), respec-

Fig. 1. SEM image showing the cross-sectional profile of a tapered-sidewall GaN mesa structure etched using (a) conditions A and (b) conditions C.

tively.

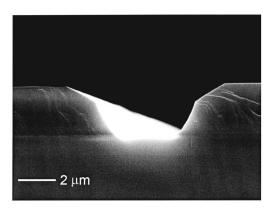

In general, a greater angle of inclination reduces the sharpness of the edge and improves step coverage. Hence, etching under conditions C would be most suitable for this purpose. However, the low etch rate achievable with this recipe places severe limitations on the depth of the mesa that can be etched. As an example, the thickness of a typical nitride-based device is  $\sim 3.5 \mu m$ . Based on a demonstrated etch rate of 767 nm/min and a selectivity of 1:2.96, the thickness of the photoresist has to be more than 10  $\mu$ m. Not only are such photoresists uncommon, but the resolution achievable with thicker photoresists is also generally lower. Hence, a two-step etch recipe based on a combination of A and C can be adopted, which can then benefit from the higher etch rates of recipe A and the isotropy of recipe C. A cross-sectional SEM image of the resultant structure is shown in Fig. 2. The two-step gradient enabled represents an improvement to the single etch procedure.

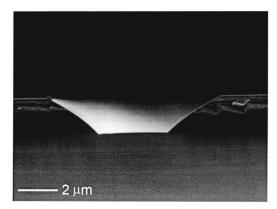

A further variation of the process involves the technique of resist reflow, commonly used for the fabrication of microlenses. After resist patterning, the samples are left on a hotplate (set at 115 °C) for 3 min. Etch recipe A is employed for this etch. The gentle gradient achieved with this process, as illustrated in Fig. 3, represents a direct transfer of resist profile onto the GaN mesa structure, enabling uniform metal coating across the entire surface. Of course, this process is not without drawbacks. From the figure, a substantial loss of critical dimension can be observed. Hence, this process is not suitable for micron-scale devices.

Fig. 2. SEM cross-sectional image of a GaN mesa structure etched using a two-step etching procedure.

Fig. 3. SEM cross-sectional image of a GaN mesa structure. The masking pattern used in this etch has been treated with a thermal-reflow process.

## B. Application to device fabrication

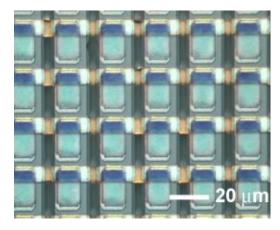

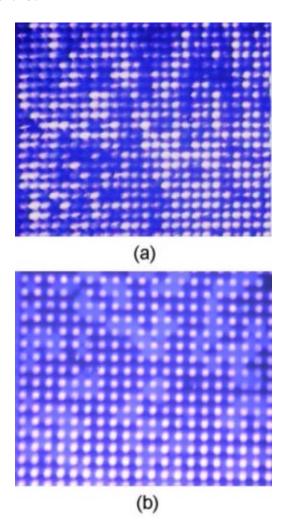

The processes developed here are targeted at the fabrication of InGaN-based microlight emitting diodes (micro-LEDs), there being linear or two-dimensional arrays of micrometer-sized LEDs. Up to now, two variants of these devices have been extensively developed with specific applications: interconnected micro-LEDs as high efficiency emitters,7 and matrix-addressable micro-LEDs for microdisplay purposes,8 at wavelengths varying from 370 nm (nearultraviolet) to 520 nm (green). Figure 4 shows the planar view of a region of a completed micro-LED array with the 135- $\mu$ m-thick Au metal lines running conformally across the 3.4  $\mu$ m mesa columns. Application of the tapered sidewall etching scheme has resulted in significant improvements to the operational performance over devices fabricated using conventional approaches as evident from the microphotographs in Fig. 5. In Fig. 5(a), the emission characteristics of an interconnected array of 12  $\mu$ m micro-LEDs emitting at a wavelength of 470 nm fabricated by the "standard" planarization technique is shown. As a result of extensive surface damage due to abrasion, the light emission pattern is extremely nonuniform. Adapting the tapered-sidewall ap-

Fig. 4. Microphotograph image of a matrix-addressable micro-LED device, fabricated using the sloped-sidewall process. Note the metal lines running conformally across the GaN columns.

Fig. 5. Comparison of the emission uniformity in interconnected micro-LED devices emitting at 470 nm fabricated using (a) planarization and (b) tapered-sidewall techniques.

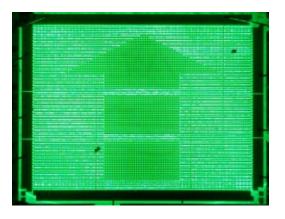

proach, light emission is uniform across the complete array, as illustrated in Fig. 5(b). Such uniformity also applies to the electrical characteristics of the devices. Using the same etching technique, microdisplays with a resolution of  $128 \times 96$  have been demonstrated, and is illustrated in Fig. 6.

Fig. 6. Operational image of a  $128 \times 96$  elements microdisplay, with an arrow pattern illuminated at a wavelength of 520 nm.

#### **JVST B - Microelectronics and Nanometer Structures**

#### IV. CONCLUSIONS

In summary, a method controllably of producing mesa structures with tapered sidewall in GaN-based materials has been introduced. ICP etching is used because of the ability to control the vertical and lateral etch components simultaneously. By adjusting a combination of parameters, tapered sidewalls can be formed, with inclination angles ranging from 25° to 40°, allowing for conformal metal coverage across the mesa structures. The process has been successfully adopted for the fabrication of interconnected and matrix-addressable micro-LEDs, where superior performance and uniformity have been achieved compared to devices fabricated using conventional techniques.

- <sup>1</sup>S. A. Smith, C. A. Wolden, M. D. Bremser, A. D. Hanser, R. F. Davis, and W. V. Lampert, Appl. Phys. Lett. **71**, 3631 (1997).

- <sup>2</sup>K. M. Geib, K. D. Choquette, D. K. Serkland, A. A. Allerman, and T. W. Hargett, IEEE J. Sel. Top. Quantum Electron. **8**, 943 (2002).

- <sup>3</sup>S. X. Jin, J. Li, J. Y. Lin, and H. X. Jiang, Appl. Phys. Lett. **77**, 3236 (2000).

- <sup>4</sup>C. W. Jeon, H. W. Choi, and M. D. Dawson, IEEE Photonics Technol. Lett. **15**, 1516 (2003).

- <sup>5</sup>H. W. Choi, S. J. Chua, A. Raman, J. S. Pan, and A. T. S. Wee, Appl. Phys. Lett. **77**, 1795 (2000).

- W. Choi, S. J. Chua, and S. Tripathy, J. Appl. Phys. **92**, 4381 (2002).

H. W. Choi, M. D. Dawson, P. R. Edwards, and R. W. Martin, Appl. Phys. Lett. **83**, 4483 (2003).

- <sup>8</sup>H. W. Choi, C. W. Jeon, and M. D. Dawson, IEEE Electron Device Lett. 25, 277 (2004).