## Improved performances of metal-oxide-nitride-oxide-silicon memory with HfTiON as charge-trapping layer

J. X. Chen, J. P. Xu, L. Liu, and P. T. Lai

Citation: Applied Physics Letters 103, 213507 (2013); doi: 10.1063/1.4829880

View online: http://dx.doi.org/10.1063/1.4829880

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/103/21?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Performance improvement of metal-Al2O3-HfO2-oxide-silicon memory devices with band-engineered Hf-aluminate/SiO2 tunnel barriers

J. Vac. Sci. Technol. B 31, 041201 (2013); 10.1116/1.4807842

Improved charge-trapping properties of TiON/HfON dual charge storage layer by tapered band structure Appl. Phys. Lett. **101**, 133503 (2012); 10.1063/1.4754830

Performance enhancement of multilevel cell nonvolatile memory by using a bandgap engineered high- κ trapping layer

Appl. Phys. Lett. 97, 253503 (2010); 10.1063/1.3531559

Device characteristics of HfON charge-trap layer nonvolatile memory

J. Vac. Sci. Technol. B 28, 1005 (2010); 10.1116/1.3481140

Electrical properties of HfTiON gate-dielectric metal-oxide-semiconductor capacitors with different Si-surface nitridations

Appl. Phys. Lett. 91, 052902 (2007); 10.1063/1.2767177

## Improved performances of metal-oxide-nitride-oxide-silicon memory with HfTiON as charge-trapping layer

J. X. Chen, <sup>1</sup> J. P. Xu, <sup>1,a)</sup> L. Liu, <sup>1</sup> and P. T. Lai<sup>2,a)</sup>

<sup>1</sup>School of Optical and Electronic Information, Huazhong University of Science and Technology, Wuhan 430074, People's Republic of China

(Received 4 May 2013; accepted 28 October 2013; published online 22 November 2013)

The properties of HfTiON as charge-trapping layer of metal-oxide-nitride-oxide-silicon memory are investigated, and effects of different Hf/Ti ratios in HfTiON films on the physical and electrical characteristics are analyzed. It is found that the higher the Ti content, the higher is the charge-trapping efficiency, thus, larger memory window and higher program/erase speeds. However, excessive Ti can diffuse to the HfTiON/SiO<sub>2</sub> interface and cause the formation of a Ti-silicate interlayer, which deteriorates the retention of data. Experimental results indicate that the device with a Hf/Ti ratio of  $\sim$ 1:1 can give a good trade-off between performance and reliability. © 2013 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4829880]

Recently, metal-oxide-nitride-oxide-silicon (MONOS) charge-trapping flash memory has attracted much concern for the next-generation nonvolatile memory application due to its advantages of low operating voltage, feasibility of scaling, and simple fabrication process. <sup>1-3</sup> Various high- $\kappa$  dielectrics, e.g., HfO<sub>2</sub>, 4,5 Ta<sub>2</sub>O<sub>5</sub>,6 ZrON,7 LaON,8 and HfGdO,9 have been investigated as the charge trapping layer (CTL) to improve the performance and reliability. Among these high- $\kappa$ materials, HfON, due to its high k value ( $\sim$ 22), good thermal stability with SiO2, deep conduction-band edge relative to  $SiO_2$  ( $\sim 1.5 \, eV$ ), and deep trap energy ( $\sim 1 \, eV$ ),  $^{10-12}$  was listed in the ITRS [The International Technology Roadmap for Semiconductors, 2009, www.itrs.net.] to replace the conventional Si<sub>3</sub>N<sub>4</sub> for further down-scaling. The main problem of HfON is its inferior trapping efficiency as compared to Si<sub>3</sub>N<sub>4</sub>. <sup>13,14</sup> Several approaches, including band engineering <sup>15</sup> and implant of dopants into HfON, 16 have been proposed to obtain a larger memory window. On the other hand, TiO2 is a high- $\kappa$  material ( $\kappa > 80$ ), which is very beneficial for further down-scaling. Also, it has been reported that incorporation of Ti atoms into the rare earth dielectric films as CTL, e.g., HfTiO<sub>4</sub>, <sup>18</sup> YbTiO<sub>5</sub>, <sup>19</sup> and Dy<sub>2</sub>TiO<sub>5</sub>, <sup>20</sup> can improve the physical and electrical properties of memory devices. In view of the above points, we investigated the physical and electrical properties of HfTiON as the CTL of MONOS flash memory. Furthermore, the Hf/Ti ratio in the HfTiON film was optimized by considering a trade-off between memory performance and reliability.

Both metal-nitride-oxide-silicon (MNOS) and MONOS capacitor memories were fabricated on p-silicon wafers with a resistivity of 1–10  $\Omega$ ·cm. After the standard Ratio Corporation of America cleaning, a 3.1-nm SiO<sub>2</sub> film was thermally grown at 900 °C in dry O<sub>2</sub>. Next, a high- $\kappa$  HfTiON film was deposited as CTL by reactive co-sputtering method using Denton Vacuum Discovery Deposition System at room temperature

(RT). In order to investigate the effects of Ti content on the charge-trapping properties of HfTiON, different Ti contents were incorporated into HfON by co-sputtering of Hf and Ti targets in a mixed ambient of  $Ar/N_2/O_2 = 12/15/3$  at a fixed Hf-target RF power of 28 W and different Ti-target DC powers (6.7 W, 14.9 W, and 29.6 W, respectively), and the corresponding samples were denoted as HTON1, HTON2, and HTON3 with an atomic Hf/Ti ratio of 3.31:1, 1:1.07, and 1:2.97, respectively, determined by normal x-ray photoelectron spectroscopy (XPS) analysis. All the HfTiON films had roughly the same thickness of 6.8 nm. Rapid thermal annealing was performed at 500 °C for 1 min in N<sub>2</sub> ambient to improve the quality of the high- $\kappa$  dielectric film. Subsequently, a 13.2-nm Al<sub>2</sub>O<sub>3</sub> as blocking layer was deposited by atomic layer deposition using Al(CH<sub>3</sub>)<sub>3</sub> as precursor and H<sub>2</sub>O as oxidant at 300 °C in an Oxford OpAL System. The corresponding MNOS capacitors without Al<sub>2</sub>O<sub>3</sub> were also prepared for constant-current stress (CCS) measurements. Finally, Al was thermally evaporated and patterned as gate electrode and also as back electrode, followed by a forming-gas annealing in  $H_2/N_2$  (5%  $H_2$ ) at 300 °C for 20 min.

The physical and electrical characteristics of the HfTiON CTL were thoroughly investigated. The film thickness was measured by multi-wavelength ellipsometry and confirmed by transmission electron microscopy (TEM) images. The elemental composition and chemical bonding were analyzed by XPS using a monochromatic Al  $K_{\alpha}$  (1486.7 eV) source. Capacitance-voltage (C-V) and CCS measurements were carried out using HP4284A precision LCR meter and HP4156A precision semiconductor parameter analyzer, respectively. The flat-band voltage ( $V_{\rm FB}$ ) of the samples was extracted by assuming  $C_{\rm FB}/C_{\rm OX} = 0.5$  ( $C_{\rm FB}$  and  $C_{\rm OX}$  are the flat-band and oxide capacitances, respectively, determined from 1-MHz high-frequency C-V curve).

Fig. 1 shows the cross-sectional TEM images of the MONOS capacitors after annealing the stacked gate dielectrics. The thickness of the HfTiON films is evaluated to be 6.8 nm, 6.7 nm, and 6.9 nm for the HTON1, HTON2, and

<sup>&</sup>lt;sup>2</sup>Department of Electrical and Electronic Engineering, the University of Hong Kong, Pokfulam Road, Hong Kong

a) Authors to whom correspondence should be addressed. Electronic addresses: jpxu@mail.hust.edu.cn and laip@eee.hku.hk.

FIG. 1. Cross-sectional TEM image of Al/Al<sub>2</sub>O<sub>3</sub>/HfTiON/SiO<sub>2</sub>/Si structure. (a) HTON1 sample, (b) HTON2 sample, and (c) HTON3 sample.

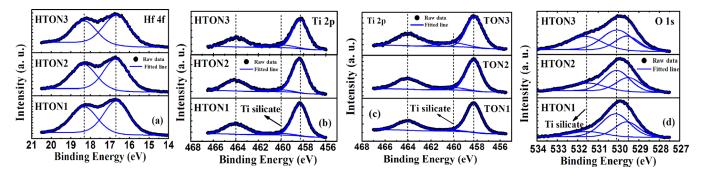

HTON3 samples, respectively. It can be observed that the HfTiON/SiO<sub>2</sub> interface is clearer and sharper for the HTON1 sample than the HTON2 and HTON3 samples, indicating better interface quality for the HTON1 sample. Moreover, no evidence of structural phase transformation can be found as the Ti content increases, i.e., all the HfTiON films should be amorphous. The XPS spectra of Hf 4f, Ti 2p, and O 1s are shown in Fig. 2. It can be seen that the chemical bonding of the three samples is almost the same, independent of the Ti-target sputtering power. Using Gaussian fitting, the Hf 4f and Ti 2p spectra can be decomposed into two and three sub-peaks, respectively. As shown in Fig. 2, the peak binding energies located at around  $18.3/16.6 \,\mathrm{eV}$  for Hf  $4f_{5/2}/\mathrm{Hf}$   $4f_{7/2}$ and 464.0/458.3 eV for Ti  $2p_{1/2}$ /Ti  $2p_{3/2}$  are assigned to be HfON<sup>21</sup> and TiON, respectively. This is fully in agreement with our previous investigation.<sup>22</sup> Moreover, Ti 2p shows a peak binding energy at 460.0 eV, which should be attributed to Ti silicate.<sup>23</sup> In fact, as shown in Fig. 2(c), for TiON films deposited on SiO<sub>2</sub> with the same Ti-target DC power and deposition ambient as the HfTiON films, the same peak at 460.0 eV is also observed, which should correspond to Ti-Si bonds and is the precursor of the Ti silicate formed during the subsequent post-deposition annealing.

To further confirm the composition of the HfTiON films with different Ti contents, the O 1s spectrum which can be decomposed into three sub-peaks is examined, as shown in Fig. 2(d). The three peaks appeared at 530.0 eV, 529.5 eV,

and 531.6 eV correspond to HfON, TiON, and Ti silicate, respectively. The peak binding energy for Ti silicate agrees with that reported by Sarkar *et al.*<sup>24</sup> From Figs. 2(b) and 2(d), it can be seen that the peak intensity corresponding to Ti silicate increases as Ti content increases, suggesting that more Ti incorporation in the HfTiON film leads to thicker interfacial layer.

The difference in charge-trapping characteristics of the HfTiON films with different Hf/Ti ratios is examined by the CCS method. A constant current of  $10 \,\mu\text{A/cm}^2$  or  $20 \,\mu\text{A/cm}^2$  is applied to the gate electrode of the MNOS capacitors for 1 s, respectively. The trapped charge centroid  $(X_t)$  and the trapped charge  $(Q_{\text{trap}})$  extracted from the CCS measurement are given as<sup>25</sup>

$$X_{t} = t_{stack} \left( 1 - \frac{\Delta V_{-g}}{\Delta V_{+g}} \right)^{-1}, \tag{1}$$

$$Q_{\text{trap}} = \frac{\varepsilon_0 \varepsilon_{stack}}{t_{stack}} \left( 1 - \frac{\Delta V_{-g}}{\Delta V_{+g}} \right), \tag{2}$$

where  $X_t$  is measured from the Al/HfTiON interface to the HfTiON/SiO<sub>2</sub> interface;  $\Delta V_{-g}$  and  $\Delta V_{+g}$  are the negative and positive gate-voltage shifts;  $t_{stack}$  and  $\varepsilon_{stack}$  are the physical thickness and equivalent dielectric constant of the HfTiON/SiO<sub>2</sub> stack, respectively. The extracted  $X_t$  and

FIG. 2. Hf 4f (a), Ti 2p (b), and O 1s (c) core level XPS spectrum of HfTiON films with different Ti contents; Ti 2p (c) core level XPS spectrum of the asdeposited TiON film under the same Ti-target DC power and deposition ambient as HfTiON deposition. The TON1, TON2, and TON3 are corresponding to HTON1, HTON2, and HTON3, respectively.

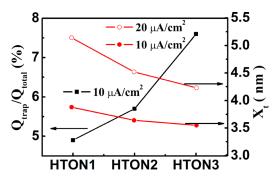

FIG. 3.  $X_t$  and  $Q_{trap}/Q_{total}$  under the constant-current stress for HfTiON MNOS capacitors with different Ti contents.

$Q_{trap}/Q_{total}$  for the HfTiON films with various Ti contents are shown in Fig. 3. The charge-trapping efficiency (defined as  $Q_{trap}/Q_{total}$ ) is increased as the incorporated Ti increases, indicating that adding Ti atoms into the HfON film can effectively improve the charge-trapping efficiency. Also as shown in Fig. 3, the  $X_t$  moves toward the HfTiON/SiO<sub>2</sub> interface as the constant-current stress increases, suggesting that the injected electrons tend to fill the traps near the Al/HfTiON interface first, which is beneficial for the retention characteristics by suppressing electrons tunneling back to the silicon substrate. <sup>12</sup>

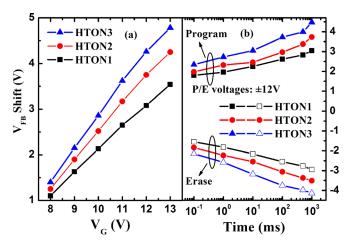

Fig. 4(a) is the memory window of the samples when HfTiON with different Ti contents is used as CTL. The largest window of 4.8 V is achieved for the HTON3 sample, as compared to 3.5 V and 4.3 V for the HTON1 and HTON2 samples, respectively, under program/erase (P/E) voltages of +/-13 V for 1 s. Obviously, the more the Ti incorporation, the larger is the memory window, further confirming the higher charge-trapping efficiency can be achieved for higher Ti content. In addition, the dielectric constant extracted from the accumulation capacitance (COX) of C-V curve (not shown here) is 18.6, 22.2, and 24.8 for the HTON1, HTON2, and HTON3 samples, respectively, indicating that the dielectric constant of the HfTiON film increases with the Ti content.<sup>26</sup> As a result, the voltage drop across the tunnel oxide is larger for the HTON3 sample than the other two samples, inducing a higher electric field across the tunnel layer, and thus more electrons injected to the HfTiON CTL. Thus, a reasonably high Ti content in the HfTiON CTL can improve the storage capability and injection efficiency of charges.

Fig. 4(b) is the transient P/E characteristic of the samples as a function of pulse width varying from 0.1 ms to 1 s. Under a P/E voltage of  $\pm 12$  V for 1 ms, the HTON3 sample shows a  $V_{FB}$  shift of 2.73/–2.58 V, which is larger than 1.96/–1.82 V for the HTON1 sample and 2.32/–2.18 V for the HTON2 sample, i.e., highest P/E speed obtained for the HTON3 sample with the highest Ti content. This is attributed to higher charge-trapping efficiency and higher charge-injection efficiency. Moreover, no significant over-erase phenomenon is observed for all the devices, implying negligible hole trapping in the CSL.  $^{27}$

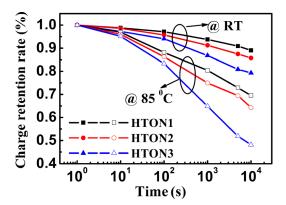

Fig. 5 is the retention characteristics of the samples under programming state (12 V for 1 s), measured at RT and 85 °C, respectively. The charge retention rate after 10<sup>4</sup> s is 89.0%, 85.8%, and 79.3% at RT, and drops to 69.4%, 64.2%, and 48.1% at 85 °C for the HTON1, HTON2, and HTON3

FIG. 4. Memory window of the MONOS capacitors under various gate biases (a) and transient P/E characteristics of the MONOS capacitors as a function of time (b).

samples, respectively. Apparently, charge loss rate is increased as the Ti content in the HfTiON CTL increases. From the results of the trapped charge centroid in Fig. 3, the memory device with higher Ti content should have better data retention because the trapped charge centroid is farther away from the HfTiON/SiO2 interface. However, excessive Ti in the HfTiON film can diffuse to the HfTiON/SiO2 interface, <sup>23</sup> leading to the formation of Ti silicate at the interface, and thus interfacial traps, which can increase the discharge of electrons through the trap-assisted tunneling mechanism. Moreover, the conduction-band offset relative to the silicon substrate decreases to less than 1 eV for the HfTiON film with a Hf/Ti ratio of 1:2,28 and so the trapped electrons in the CTL can tunnel back to the silicon substrate more easily, causing the degradation of the retention characteristics. Further deterioration in the data retention at 85 °C indicates that more electrons in the HfTiON CTL can obtain sufficient thermal energy to go through the tunnel oxide to the Si substrate. Therefore, the Ti content in the HfTiON film should be carefully chosen to obtain a good trade-off between memory performance and reliability. For example, the HTON2 sample with a Hf/Ti ratio of 1:1.07 has a large memory window of 4.25 V at  $\pm 13 \text{ V}$ , high P/E speed with 2.32/-2.18 Vat  $\pm 1/-12$  V for 1 ms, and good data retention of 85.8% at room temperature and 64.2% at 85 °C.

FIG. 5. Retention characteristics of HfTiON memory devices measured at RT and 85 °C.

TABLE I. Comparison of memory performances between the HfTiON CTL in this work and other HfXON CTL (X denotes other metal).

| Stacked gate structure                                                                   | Dielectric constant | Memory<br>window (V)                               | Program/erase V <sub>FB</sub> shift (V)                                                       | Retained charge<br>after 10 yr (%) |

|------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------|

| Al/Al <sub>2</sub> O <sub>3</sub> /HfTiON/SiO <sub>2</sub> /Si (HTON2) (13.2/6.8/3.1 nm) | 22.2                | $3.75  \text{V@} \pm 12  \text{V},  1  \text{s}$   | 2.32 V@ + 12 V, 1 ms                                                                          | 85.8% @RT<br>64.2% @85°C           |

|                                                                                          |                     |                                                    | -2.18V@ $-12V$ , 1 ms                                                                         |                                    |

| Al/Al <sub>2</sub> O <sub>3</sub> /HfYON/SiO <sub>2</sub> /Si (Ref. 12) (20/12/3 nm)     | NA                  | $6.0\mathrm{V}$ @ $\pm 14\mathrm{V}$ , 1 s         | 2.9 V@ + 12 V, 1 ms<br>NA                                                                     | 79%@RT                             |

| Al/ HfLaON/SiO <sub>2</sub> /Si (Ref. 29) (15/3 nm)                                      | 17.6                | $3.25 \mathrm{V@} \pm 12 \mathrm{V}, 1 \mathrm{s}$ | $1.5  \text{V@} + 10  \text{V}, 1  \text{ms} \\ -1.1  \text{V@} - 10  \text{V}, 1  \text{ms}$ | 66%@RT                             |

To demonstrate the potential of Ti incorporation into HfON, a comparison of memory performances between the HfTiON CTL in this work and other HfXON CTL<sup>12,29</sup> (X denotes other metal) is given in Table I. It can be seen that based on a comprehensive evaluation, the HfTiON CTL exhibits good memory performances and thus has promising application for nonvolatile memory devices.

The effects of Ti incorporation in HfON on the physical and electrical properties of MONOS capacitor memory with HfTiON as CTL are investigated. It is found that increasing the Ti content will induce higher charge-trapping efficiency, thus improving the memory window and P/E speeds. However, the data retention characteristics are degraded. Therefore, the Ti content in the HfTiON film needs to be optimized to achieve a good trade-off between performance and reliability. In this work, the MONOS memory with a Hf/Ti ratio of  $\sim$ 1:1 in the HfTiON CTL exhibits a large memory window, high P/E speed, and good data retention. In summary, high- $\kappa$  HfTiON with an optimal Ti content has high potential as the CTL of the MONOS memory device.

This work was financially supported by the National Natural Science Foundation of China (Grant No. 60976091) and the University Development Fund (Nanotechnology Research Institute, No. 00600009) of the University of Hong Kong.

- <sup>7</sup>C. Y. Tsai, T. H. Lee, C. H. Cheng, A. Chin, and H. Wang, Appl. Phys. Lett. **97**, 213504 (2010).

- <sup>8</sup>X. D. Huang, J. K. O. Sin, and P. T. Lai, IEEE Trans. Device Mater. Reliab. **12**, 306 (2012).

- <sup>9</sup>J. C. Wang, C. T. Lin, P. C. Chou, and C. S. Lai, Microelectron. Reliab. **52**, 635 (2012).

- <sup>10</sup>S. H. Jeon, Electrochem. Solid-State Lett. **12**, H412 (2009).

- <sup>11</sup>T. Lee and S. K. Banerjee, J. Vac. Sci. Technol. B 28, 1005 (2010).

- <sup>12</sup>X. D. Huang, L. Liu, J. P. Xu and P. T. Lai, Appl. Phys. Lett. 99, 112903 (2011).

- <sup>13</sup>C. H. Lai, A. Chin, H. L. Kao, K. M. Chen, M. Hong, J. Kwo, and C. C. Chi, Dig. Tech. Pap. Symp. VLSI Technol. 2006, 44.

- <sup>14</sup>S. H. Lina, A. Chin, F. S. Yeh, and S. P. McAlister, Tech. Dig. -Int. Electron Devices Meet. 2008, 1.

- <sup>15</sup>X. D. Huang, P. T. Lai, and J. K. O. Sin, Microelectron. Reliab. **52**, 2527 (2012).

- <sup>16</sup>C. Y. Tsai, T. H. Lee, and A. Chin, IEEE Electron Device Lett. 32, 381 (2011).

- <sup>17</sup>L. Q. Zhu, L. D. Zhang, and Q. Fang, Appl. Phys. Lett. **91**, 172902 (2007).

<sup>18</sup>C. H. Kao, H. Chen, H. W. Chang, and C. S. Chuang, J. Vac. Sci. Technol.

- A **29**, 06B102 (2011).

19T. M. Pan, J. S. Jung, and X. C. Wu, Appl. Phys. Lett. **96**, 162901 (2010).

- <sup>20</sup>F.-H. Chen and T.-M. Pan, J. Electron. Mater. **41**, 2197 (2012).

- <sup>21</sup>X. Gaobo and X. Qiuxia, in 9th International Conference on Solid-State and Integrated-Circuit Technology (ICSICT) (2008), p. 1284.

- <sup>22</sup>L. Liu, J. P. Xu, F. Ji, J. X. Chen, and P. T. Lai, Appl. Phys. Lett. 101, 133503 (2012).

- <sup>23</sup>M. Liu, L. D. Zhang, G. He, X. J. Wang, and M. Fang, J. Appl. Phys. 108, 024102 (2010).

- <sup>24</sup>D. K. Sarkar, E. Desbiens, and M. A. El Khakani, Appl. Phys. Lett. 80, 294 (2002).

- <sup>25</sup>M. H. Jung, K. S. Kim, G. H. Park, and W. J. Cho, Appl. Phys. Lett. 94, 053508 (2009).

- <sup>26</sup>H. X. Xu, J. P. Xu, C. X. Li, C. L. Chan, and P. T. Lai, Appl. Phys. A **99**,

- <sup>27</sup>L. Liu, J. P. Xu, F. Ji, J. X. Chen, and P. T. Lai, Appl. Phys. Lett. **101**, 033501 (2012).

- <sup>28</sup>G. He, Z. Q. Sun, Y. Q. Ma, M. Z. Wu, Y. M. Liu, S. W. Shi, G. Li, X. S. Chen, L. D. Zhang, and Z. B. Fang, Semicond. Sci. Technol. 26, 105019

- <sup>29</sup>L. Liu, J. P. Xu, F. Ji, X. D. Huang, and P. T. Lai, IEEE Trans. Device Mater. Reliab. 11, 244 (2011).

<sup>&</sup>lt;sup>1</sup>G. Wang and M. H. White, Solid-State Electron. **52**, 1491 (2008).

<sup>&</sup>lt;sup>2</sup>X. D. Huang, J. K. O. Sin, and P. T. Lai, IEEE Trans. Electron Devices 58, 4235 (2011).

<sup>&</sup>lt;sup>3</sup>C. Y. Tsai and A. Chin, IEEE Trans. Electron Devices **59**, 252 (2012).

<sup>&</sup>lt;sup>4</sup>H.-W. You and W.-J. Cho, Appl. Phys. Lett. **96**, 093506 (2010).

<sup>&</sup>lt;sup>5</sup>S. Spiga, F. Driussi, A. Lamperti, G. Congedo, and O. Salicio, Appl. Phys. Express **5**, 021102 (2012).

<sup>&</sup>lt;sup>6</sup>C. H. Cheng and J. Y. M. Lee, Appl. Phys. Lett. **91**, 192903 (2007).