# Memristive Crossbar Arrays for Storage and Computing Applications

Huihan Li, Shaocong Wang, Xumeng Zhang, Wei Wang, Rui Yang, Zhong Sun, Wanxiang Feng, Peng Lin, Zhongrui Wang,\* Linfeng Sun,\* and Yugui Yao

The emergence of memristors with potential applications in data storage and artificial intelligence has attracted wide attentions. Memristors are assembled in crossbar arrays with data bits encoded by the resistance of individual cells. Despite the proposed high density and excellent scalability, the sneak-path current causing cross interference impedes their practical applications. Therefore, developing novel architectures to mitigate sneak-path current and improve efficiency, reliability, and stability may benefit next-generation storageclass memory (SCM). Moreover, conventional digital computers face the von-Neumann bottleneck and the slowdown of transistors' scaling, imposing a big challenge to hardware artificial intelligence. Memristive crossbar features colocation of memory and processing units, as well as superior scalability, making it a promising candidate for hardware accelerating machine learning and neuromorphic computing. Herein, first, crossbar architecture is introduced. Then, for storage, the origin of sneak-path current is reviewed and techniques to mitigate this issue from the angle of materials and circuits are discussed. Computing wise, the applications of memristive crossbars in both machine learning and neuromorphic computing are surveyed, focusing on the structure of unit cells, the network topology, and the learning types. Finally, a perspective on future engineering and applications of memristive crossbars is discussed.

### 1. Introduction

Computers nowadays feature a wellestablished memory hierarchy, usually including solid-state drives enabled by floating-gate transistors for nonvolatile data storage, off-chip dynamic random-access memory (DRAM), and on-chip caches and register files such as those based on static random-access memory (SRAM). The reason for such a hierarchy is the performance gap between floating-gate transistors, DRAMs, and SRAMs. The nonvolatile floating-gate transistor has slow speed and high energy consumption in programming, in addition to the very limited endurance. The volatile DRAM is relatively speedy and energy saving in programming. The volatile SRAM is the fastest and the most energy efficient among the three but at the cost of a large footprint. An ultimate pursuit of the memory community is to come up with a unified memory solution that is nonvolatile like a floatinggate transistor, featuring fast and low-energy programming like an SRAM. Such memory is not yet commercially available.

H. Li, Prof. W. Feng, Prof. L. Sun, Prof. Y. Yao Centre for Quantum Physics Key Laboratory of Advanced Optoelectronic Quantum Architecture and Measurement (MOE) School of Physics Beijing Institute of Technology Beijing 100081, China E-mail: sunlinfeng@bit.edu.cn

H. Li, Prof. W. Feng, Prof. L. Sun, Prof. Y. Yao Beijing Key Lab of Nanophotonics & Ultrafine Optoelectronic Systems School of Physics Beijing Institute of Technology Beijing 100081, China

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/aisy.202100017.

© 2021 The Authors. Advanced Intelligent Systems published by Wiley-VCH GmbH. This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

#### DOI: 10.1002/aisy.202100017

S. Wang, Prof. Z. Wang Department of Electrical and Electronic Engineering The University of Hong Kong Pokfulam Road, Hong Kong E-mail: zrwang@eee.hku.hk

Dr. X. Zhang Frontier Institute of Chip and System Fudan University Shanghai 200438, China

Dr. W. Wang The Andrew and Erna Viterbi Department of Electrical Engineering Technion – Israel Institute of Technology Haifa 32000, Israel

Prof. R. Yang University of Michigan – Shanghai Jiao Tong University Joint Institute Shanghai Jiao Tong University Shanghai 200240, China

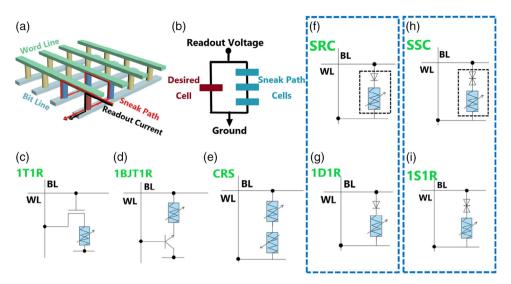

**Figure 1.** Crossbar architecture and the potential issues on sneak-path current, as well as the potential solutions. a) Schematic illustration of the crossbar memory array architecture, with normal and sneak current paths, respectively. b) The equivalent electric circuit of sneak current is involved in the crossbar array. c-i) Seven types of possible solutions to solve the sneak-path current issue, including 1T1R, 1BJT1R, CRS, 1D1R, 1S1R, SRC, and SSC, respectively.

Another limitation of digital computers is the von Neumann architecture, where the physically separated memory and computing units incur large latency and high energy consumption due to data shuttling.<sup>[1–5]</sup> This is more evident in machine learning and neuromorphic computing due to frequent transfer of massive network parameters. In contrast, our brain computes in a drastically different way, in which the information is processed and stored at the same place, thanks to the massively intertwined neurons and synapses.<sup>[6–13]</sup> Numerous efforts have been made to build an electronic brain using traditional complementary metal—oxide—semiconductors (CMOS).<sup>[14–16]</sup> However, no digital computing systems can simultaneously parallel the intelligence and efficiency of a human brain yet.<sup>[9,10,17]</sup> This is further intensified by the slowdown of Moore's law, because the size of transistors is approaching their physical limit.<sup>[9,15]</sup> Therefore, fundamental changes to the computing paradigm are required.

A memristor, revealed as the fourth passive electronic element, is a tunable resistor with memory as conceived by Professor Chua<sup>[18,19]</sup> and demonstrated by researchers from Hewlett-Packard (HP) lab.<sup>[20]</sup> The HP memristor is essentially a resistive switch which consists of a dielectric layer sandwiched by two electrodes. The unique feature of memristors is that the conductance depends on historical electrical signals, making them capable of working as nonvolatile memory. In addition, memristors may store multibit information with continuously tunable conductance, in contrast to binary states "0" and "1" in traditional digital storage systems, equipping them with higher bit density. Nonvolatility, fast programming, low

Prof. Z. Sun Institute for Artificial Intelligence Institute of Microelectronics Peking University Beijing 100871, China programming energy, and compact footprint<sup>[21–23]</sup> make memristors a promising solution for the next-generation embedded memory, which may combine the advantage of SRAM and floating-gate transistors. In addition to memory and storage, memristors intrinsically mimic the dynamic behaviors of synapses and neurons, thanks to the bias-history-dependent conductance, which has led to various memristor-based artificial and spiking neural networks (SNNs).<sup>[24–28]</sup>

The simple two-terminal metal-insulator-metal (MIM) structures of memristors make them capable of being integrated into dense crossbar arrays.<sup>[29,30]</sup> As shown in **Figure 1**a, a typical crossbar array consists of parallel metal lines, termed word lines and bit lines, respectively, as the top and bottom electrodes that are perpendicular to each other. The two-terminal memristors are formed at the intersections of word and bit lines. The red cylinder represents a selected cell during the operation to read its conductance (the black solid line). In this readout process, as shown in Figure 1a, a sneak path, represented by the red solid line, carries unwanted current, which is equivalent to series resistors that are parallel to the selected memristor, as shown in Figure 1b. Such sneak paths would lead to extra energy consumption from unselected cells, which also degrades the read margin and thus limits the size of arrays. It shall be noted that the sneak current issue, which is prominent in sequential read-and-write isolated memristors in crossbar arrays, would have a less critical impact on both machine learning and neuromorphic computing.<sup>[31]</sup> So far, extensive research has been reported to address this sneak-path leakage current in resistive

Prof. P. Lin

College of Computer Science and Technology Zhejiang University Hang Zhou 310013, China

www.advintellsyst.com

random-access memory (RRAM) and phase-change memory (PCM) arrays. Such solutions include engineering the unit cells, such as introducing an access element to the 1-memristor (1R) cell to form composite cells like one-transistor-one memristor (1T1R), one diode-one memristor (1D1R), one selector-one memristor (1S1R), self-rectifying memristors, etc.<sup>[32–35]</sup> The introduction of the access device not only improves energy efficiency during array programming, but may also assist memristors in implementing synaptic plasticity, thus enabling novel analog machine learning and neuromorphic computing.<sup>[36–40]</sup>

DVANCED

www.advancedsciencenews.com

In this Review, we explore the low-dimensional materials for memristive arrays, which are promising as the next-generation computing technology. In particular, with the recently reported study on the wafer-scale growth ability of low-dimensional materials,<sup>[41-43]</sup> a complete Review on the recent works including research on both low-dimensional materials and traditional materials-based memristive arrays for information storage and neuromorphic computing becomes essential. Moreover, we present a comprehensive Review of the memory unit cell design for RRAMs and PCMs to resolve the sneak-path current issue, including 1S1R, 1T1R, 1D1R, one-bipolar-junction transistor (BJT)-one memristor (1BJT1R), self-selective cell (SSC), self-rectifying cell (SRC), and complementary resistive switching (CRS) cell, as schematically shown in Figure 1c-i. The types of bias schemes and the influence of wire resistances on the read/write operations are discussed. Some of the recently reported devices with staircase output electrodes and pillar input electrodes have been proposed, which should be noted as well.<sup>[44]</sup> Finally, we survey the literature on how 1R and 1T1R arrays physically accelerate machine learning and neuromorphic computing, for example, how they implement different types of neural network topologies and how they perform different types of learning (e.g., supervised, unsupervised, and reinforcement learning, which is either implemented offline or online).

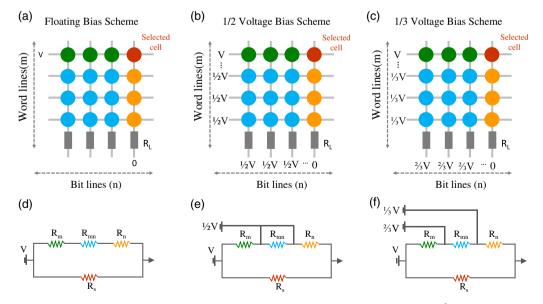

## 2. RRAM Writing/Reading Voltage Schemes in the Crossbar Arrays

To avoid programming interference, different bias schemes, as shown in Figure 2, have been proposed to bias the unselected cells with a fraction of the selected cell voltage.<sup>[45-48]</sup> Despite the pursuit of memristors with ultralow "off" current/conductance for memory cells in the crossbar arrays, the choice of bias scheme for writing/reading processes could be helpful to mitigate the sneak-path current issue. The voltage schemes could be classified based on the voltages applied to the unselected bit and word lines when the selected cell is always kept under full voltage bias. As shown in Figure 2a,d, the floating scheme leaves all the unselected word and bit lines floating. The read margin of the floating scheme could be much lower than that of the 1/2V scheme because all the sneak currents of the unselected cells will flow toward V if they cannot be suppressed appropriately. In other words, if the sneak current issue in the floating scheme is successfully handled, the crossbar RRAM in the floating scheme can exhibit better energy efficiency while achieving an extremely high density, which is mainly determined by its read margin. In the 1/2 V bias scheme, as shown in Figure 2b, e, the selected word line and selected bit line are applied with full voltage and 0 V, respectively, and the unselected word lines and bit lines are applied with 1/2 V. Thus, the selected cell (red circle) is under V bias, half-selected cells (green and yellow circles) are under  $^{1}/_{2}V$ , and the unselected cells (blue circles) are under 0 V. However, for the 1/3 V bias scheme, shown in Figure 2c,f, the selected word line and selected bit line are applied with full voltage and 0 V, respectively, same as the situation of 1/2 V. The unselected word lines are applied with 1/3 V, whereas the unselected bit lines are applied with  $^2/_3$  V. Thus, the selected memory cell (red circle) is under V bias, half-selected memory cells (green and yellow circles) are under  $^{1}/_{3}$  V bias, and the unselected memory cells (blue circles) are under  $-\frac{1}{3}$  V bias.

**Figure 2.** Three typical types of bias voltage (V) schemes. a) The floating bias scheme. b) The one-half voltage  $\binom{1}{2}$ V) bias scheme. c) The one-third voltage  $\binom{1}{3}$ V) bias scheme. d–f) The equivalent electric circuits corresponding to the three types of voltage biasing schemes, as shown in (a–c).

Therefore, developing nonlinear I-V curves with a large on/off ratio and ultralow off-state current would be promising to decrease the energy consumption.

### 3. Solutions to the Sneak-Path Current Problem in Crossbar Arrays

#### 3.1. 1S1R Cell and Crossbar Array

www.advancedsciencenews.com

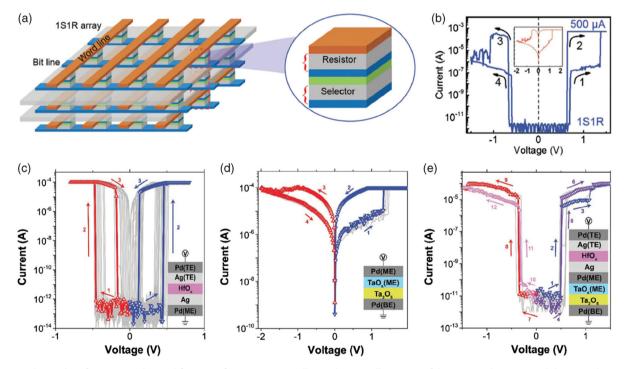

1S1R cell, a two-terminal circuit consisting of one selector and one memristor in series, as shown in Figure 3a, could lead to high-density integration, thanks to 3D stacking ability.<sup>[49-52]</sup> 1S1R device structure is considered as the most preferable scheme for high-density 3D integration of RRAM.<sup>[34,35,53-55]</sup> The ideal selector should have high conductance at a large voltage (on state) and small current (off state) at low voltage simultaneously or a highly nonlinear I-V characteristic, <sup>[56–58]</sup> as well as a small variation of threshold voltage and hold voltage.<sup>[59,60]</sup> Moreover, the selectors should be compatible with the memory cell, in terms of operating current and voltage ranges, to ensure limited sneak-path current from the unselected memory elements during both read and write operations,<sup>[34,35]</sup> as well as enough current to "set" and "reset" memristors. The selectors should also be fast enough to avoid slowing down the operation of memory devices and have high reliability with cycling endurance, array yield, and device variability comparable with that of the memristors.<sup>[34,35]</sup>

Compared with unit cells and transistors,<sup>[61,62]</sup> which are very challenging to be stacked vertically, and thus have limited ultimate density.<sup>[49]</sup> the selector is actually a bidirectional highly nonlinear resistor and is promising for high-density integration. Various material systems showing the function of selectors have been intensively studied, like silicon-based selectors,<sup>[63–66]</sup> MIMbased selectors,<sup>[67–72]</sup> ovonic threshold switching selectors,<sup>[73–78]</sup> metal-insulator transition (MIT)-based selectors.<sup>[79-84]</sup> fieldassisted superlinear threshold selectors,<sup>[85,86]</sup> and mixed ionic– electron conduction selectors.<sup>[87–91]</sup> Each of them has its merits and demerits, which have been discussed in detail by Aluguri et al.<sup>[35]</sup> Moreover, to avoid the hard breakdown of materials used for selectors, self-compliance with great nonlinearity properties is desirable for high-density crossbar array applications.<sup>[92,93]</sup> Figure 3b shows a typical nonlinear I-V curve measured from an integrated 1S1R cell with an MIM-based selector. The selector enables the low off current at around  $10^{-12}$  A and the memory window around four orders of magnitude. In this particular case, the selector turns to on-state at around 0.7 V, and the memory cell turns to on-state at 1.3 V. The following positive sweep verifies the low-resistance state (LRS) of the integrated unit. For the negative voltage sweep, the selector turns to on state at about -0.7 V and the resistance of the united cell goes back to an off state. Figure 3c-e shows the details of the nonlinear I-Vcurves from the selector, resistive memory, and their integrated cell, respectively, giving a direct impression of how to generate the nonlinear I-V curve with a 1S1R device structure from the separated selector and memory device. The device structure of

**Figure 3.** Electrical performance and typical features of 1S1R memory cell. a) Schematic illustration of the 3D crossbar array and the inset showing the structure of the memory cell with the integration of 1S and 1R. b) *I–V* curves of the 1S1R memory cell integrating the Cu/HfO<sub>2</sub>/Pt memory and a discrete-defect graphene selector under 500  $\mu$ A compliance current level. The inset shows the typical electrical characterization of the Cu/HfO<sub>2</sub>/Pt memory device. Reproduced with permission.<sup>[52]</sup> Copyright 2018, Wiley-VCH. c) Continuous bidirectional threshold switching of the individual Pd/Ag/HfO<sub>x</sub>/Ag/Pd selector. d) Repeated bipolar *I–V* switching curves of the individual memristor with the structure of Pd/Ta<sub>2</sub>O<sub>5</sub>/TaO<sub>x</sub>/Pd memristor. e) DC *I–V* curves of the integrated selector and memristor vertically. Reproduced with permission.<sup>[51]</sup> Copyright 2017, Wiley-VCH.

**ADVANCED** SCIENCE NEWS \_\_ www.advancedsciencenews.com

the selector opens another general method for designing a selector device using a structurally symmetric  $Pd/Ag/HfO_x/Ag/Pd$  stack.

#### 3.2. 1T1R Cell and Crossbar Array

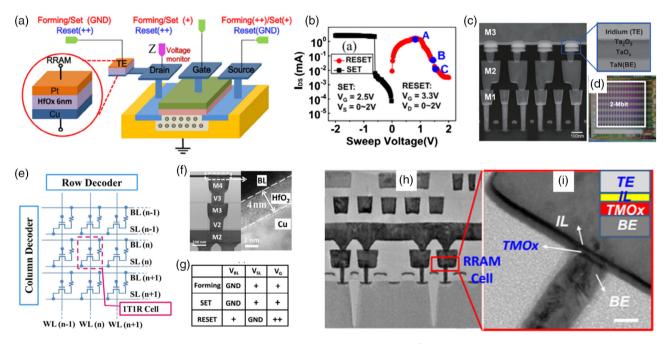

1T1R cell structure remains the most popular choice for RRAM or PCM arrays. The 1T1R crossbar architecture shares a large similarity with that of DRAM. Figure 4a,b shows the schematic of a typical 1T1R structure and the corresponding I-V curve.<sup>[94]</sup> The transistor not only allows flexible selection of memory cells but also facilitates the programming for computing-in-memory applications. For 1T1R RRAM crossbars, the cells can either be of an electrochemical metallization type (relying on the electrochemical dissolution and deposition of an active electrode metal to perform the resistive switching operation) or valence-change type (modification of the valence state of anions to induce changes in electrical conductivity, driven by underlying ion transport and redox processes). The former type was developed by Otsuka et al., reporting a 4 Mb 1T1R RRAM macro that builds on the 180 nm process of Sony. The RRAM cell consists of CuTe-based conductive material and a thin GdO<sub>x</sub> layer as the host dielectric. The macro has demonstrated a  $2.3 \text{ Gb s}^{-1}$  read throughput and a  $216 \text{ Mb s}^{-1}$  write throughput.<sup>[95]</sup> The same RRAM device was used by Fackenthal et al. in a test chip of 16 Gb 1T1Rs using the 27 nm process of Micron, achieving a

similar read throughput of  $1\,Gb\,s^{-1}$  and a write throughput of  $200\,MB\,s^{-1}.^{[96]}$

In contrast, more works have been conducted in regard to the valence-change 1T1R RRAM crossbars, as valence-change RRAMs usually have a larger activation energy of ion migration and thus better reliability. Some of the widely reported material systems with valence change, such as Hf, Ti, and Ta-based transition metal oxides, have been paired with planar transistors. For example, for Hf-based RRAMs, Sheu et al. reported a 4 Mb 1T1R macro built on the 180 nm process of TSMC, with a TiN/Ti/HfO2/TiN RRAM structure that has a cross section of  $640 \text{ nm} \times 640 \text{ nm}$ . The same RRAM also revealed four-level conductance that can encode multiple bits per cell.<sup>[97]</sup> A similar RRAM material stack was reported by Ho et al. in 1T1R arrays built on Winbond 90 nm process, showing improved reliability and high-temperature compatibility.<sup>[98]</sup> In addition, Chou et al. from TSMC reported an 11 Mb HfO<sub>x</sub>-based RRAM 1T1R macro, which was produced using the 40 nm logic process for embedded memory applications. The macro featured a RRAM programming scheme that balanced the data retention and programming energy/time, which also showed robust switching behavior in a wide range of temperatures.<sup>[99]</sup> For Ti-based cells, Chang et al. designed a 4 Mb RRAM macro for embedded memory application based on TSMC 64 nm technology. The macro was equipped with on-chip low-voltage current sense amplifiers, which worked with TiN/TiON/SiO2/Si RRAMs.<sup>[100]</sup> The same RRAM stack was also integrated with TSMC 28 nm high-ĸ MG CMOS process to build a 1 Mb 1T1R RRAM macro. The advanced technology node reduced

**Figure 4.** Nonvolatile memory based on one-transistor-one-resistor structure. a) Schematic of a typical 1T1R structure using a standard 0.13  $\mu$ m logic process and integrated with memory cell based on a Cu/HfO<sub>x</sub>/Pt structure. Reproduced with permission.<sup>[94]</sup> Copyright 2014, IEEE. b) The corresponding *I–V* curve for the 1T1R cell is shown in (a) in drain voltages (V<sub>d</sub>) sweeping mode. c) The cross-sectional TEM image of 40 nm Ir/Ta<sub>2</sub>O<sub>5</sub>/TaO<sub>x</sub>/TaN resistive memory. Ir and TaN are top and bottom electrodes, respectively. d) The image of a 2 Mbit memory array with 40 nm 1T1R TaO<sub>x</sub>-based RRAM. Reproduced with permission.<sup>[103]</sup> Copyright 2015, IEEE. e) The schematic of the 32 × 32 1T1R array based on Cu/HfO<sub>2</sub>/Pt structure reported by Lv et al. The gates of the regularly arranged transistors and the top electrodes of the memory cells were connected by the word line and bit line, respectively. f) The corresponding cross-sectional TEM image of 1T1R structure. The transistor was fabricated with the same processes as shown in (a). g) The test conditions of the ECM cell. Reproduced with permission.<sup>[108]</sup> Copyright 2015, Nature Publishing Group. h) The partial cross section of the memory cell in the 1 Mb-embedded RRAM macro. i) The zoom-in image of the memoristive cell. Reproduced with permission.<sup>[109]</sup> Copyright 2017, IEEE.

the size of the RRAM down to 0.0308  $\mu$ m<sup>2</sup> cell<sup>-1</sup>. The macro also featured improved sense margin and a low-energy RRAM programming scheme.<sup>[101]</sup> For Ta-based RRAMs, Hawahara et al. from Sony reported a 512 Kb 1T1R RRAM macro consisting of Ir/Ta<sub>2</sub>O<sub>5</sub>/TaO<sub>x</sub>/TaN RRAM cells. The macro was fabricated using the 180 nm process, which also consisted of a special two-step forming scheme that could better control the filament size and thus lead to improved endurance (10<sup>7</sup>).<sup>[102]</sup> The same RRAM device was used in a 2 Mb 1T1R RRAM macro using both 28 and 40 nm process by Hayakawa et al., which used a special process to confine the filament position to the center of the RRAM to improve reliability for embedded system applications (Figure 4c,d).<sup>[103]</sup>

ADVANCED SCIENCE NEWS \_\_\_\_\_ www.advancedsciencenews.com

For 1T1R PCM crossbars, the mature Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> cells are widely reported. In addition, developing special material combinations that can enhance reliability is also a hot research topic. For example, Close et al. reported a 4 Mbit 1T1R PCM macro built on a 90 nm process. The PCM cells were based on doped-Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> that showed multilevel conductance operation capability.<sup>[104]</sup> A similar 4 Mb 1T1R PCM macro was reported by Sandre et al., which also used a 90 nm process and Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> PCMs, featuring a 1 Mb s<sup>-1</sup> write throughput.<sup>[105]</sup>

In addition to planar transistors, valence-charge RRAM 1T1R also shows good compatibility with fin field-effect transistor (FinFET) technology, which is suitable for embedded memory applications at advanced nodes. For example, Pan et al. demonstrated the first FinFET 1T1R RRAM crossbar array using a 16 nm process of TSMC. The HfO<sub>x</sub> RRAM was realized using a similar process as that of the gate stack of a FinFET, with a cell size as small as  $0.07632 \,\mu m^{2}$ .<sup>[106]</sup> Jain et al. from Intel showed a case of 3.6 Mb 1T1R RRAM macro using the 22 nm FinFET process. It has achieved one of the largest device densities and the shortest sense time, as well as a low bit-error rate in RRAM programming across a wide range of temperatures.<sup>[107]</sup> The failure and cycled retention loss in HfO2-based electrochemical metallization memory (ECM) cell device with 1T1R structure was systematically investigated by Lv et al. using a 1 Kbit device array (Figure 4e-g), which paves the way for understanding the mechanism of endurance and retention failure.<sup>[108]</sup>

The 1T1R fabrication cost can also be minimized by engineering the device's structure design. For RRAM, as reported by Lv et al., a 1 Mb 1T1R macro, using transition metal oxide-based RRAM, was developed using a 28 nm Semiconductor Manufacturing International Corporation (SMIC) process with a single extra mask for the integration of RRAMs at small fabrication cost, as shown in Figure 4h,i. The macro shows decent switching performance and high-temperature stability for embedded memory applications.<sup>[109]</sup> For PCM, Wu et al. demonstrated that only two extra masks were needed for 1T1R PCM integration, which also allows extra footprint shrinking in a 1 Mb 1T1R PCM macro using TSMC 40 nm process. The shrinkage and electrode material engineering lead to low-write current and good resistance control with applications for computing-in-memory.<sup>[110]</sup>

#### 3.3. 1D1R Cell and Crossbar Array

Similar to 1S1R, the 1D1R structure consists of a diode and a unipolar memristor. They could achieve a footprint of  $4F^2$ , like that of 1R or 1S1R, and may further increase the structure

density to  $n/4F^{2,[111-114]}$  Due to the self-rectifying function of the diode, the reading error could be avoided as the current mainly passes through the selected memory cell itself.<sup>[115-117]</sup> Thus, 1D1R crossbar arrays feature better 3D stack ability thanks to the simple structure and CMOS process compatibility of the diode selectors. The International Technology Roadmap for Semiconductors (ITRS) also suggested that the combination of a diode and transistor with a resistor in a single chip is indispensable for the prevention of this undesired sneak-path current issue.<sup>[118]</sup> The architecture of 1D1R or 1T1R can improve reading accessibility in an integrated memory array structure,<sup>[112,119-121]</sup> whereas the 1D1R architecture is preferred in terms of integration because it occupies less area, and the design and fabrication of 1D1R devices are simpler than that for 1T1R devices.

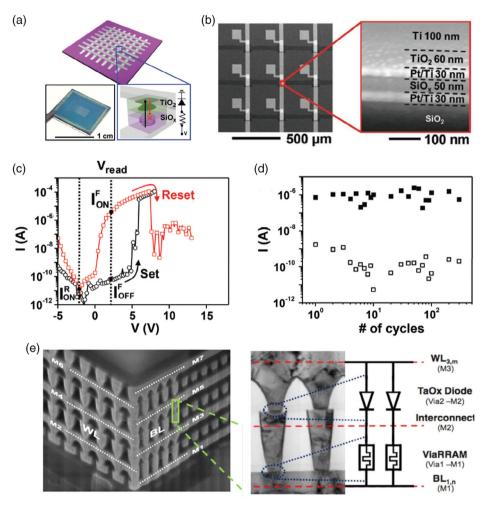

Based on the types of materials for fabricating diodes, the reported 1D1R could be classified as Si-based diodes.[122-124] organic diodes, and oxide diodes. Each of them has its own advantages and disadvantages. For example, Si-based diodes require a high-temperature process for dopant activation or enhanced contact properties, risking the rest of the fabrication processes, particularly that of memristors. Organic diodes could not be fully compatible with conventional semiconductor processes due to their vulnerability to high-temperature treatment.<sup>[125-128]</sup> Oxide-based diodes have no CMOS compatibility issue. They can also be fabricated with relatively low-temperature processes; <sup>[114,123,124,129–133]</sup> for example, Yoon et al. reported a 1D1R crossbar array shown in Figure 5a using physical vapor deposition methods at low temperature.<sup>[134]</sup> The top-view and cross-sectional scanning electron microscopy (SEM) images are shown in Figure 5b, showing the device structure consisting of Ti/TiO<sub>2</sub>/Pt/SiO<sub>x</sub>/Pt. The corresponding initial I-V curve of the fabricated 1D1R device is shown in Figure 5c and its rectification ratio at V = 2 V is around  $4 \times 10^5$ . The endurance test with set/reset/read voltages at 8/15/2 V, respectively, is shown in Figure 5d as well. However, this 1D1R configuration has not fully met the requirements of large rectification, high on/off resistance ratios, and low power consumption needs.

So far, there have been some 1D1R memristive arrays reported with a large-scale capacity based on oxide-based diodes. For example, Kawahara et al. from Panasonic reported an 8 Mb RRAM macro made of two-layer 3D-stacked 1D1R crossbars using 180 nm technology. Each 1D1R cell consists of an Ir/Ta2O5/TaOx/TaN RRAM paired with a bidirectional TaN/ SiN<sub>x</sub>/TaN diode, with a writing throughput up to  $443 \text{ Mb s}^{-1}$ .<sup>[135]</sup> The density of the storage can be further increased with an advanced technology node. Hsieh et al. demonstrated a three-layer 1D1R RRAM crossbar using TSMC 28 nm HKMG CMOS Cu line process. The material stack of the RRAM is Ta/TaN/TaON/Cu, which is paired with a  $TaO_x$  diode, as shown in Figure 5e.<sup>[136]</sup> Liu et al. unveiled a 32 Gb 1D1R RRAM test chip, which is one of the largest capacity RRAM chips developed so far. The chip has two-layer stacked metal oxide RRAM and diodes, fabricated using the 24 nm technology of Sandisk and Toshiba.<sup>[137]</sup>

However, due to the rectifying characteristic of the diode, almost all 1D1R arrays use unipolar memristors, because bipolar memristors demand both positive and negative voltage polarities for switching.<sup>[116,138–141]</sup> Further, the device performance of

www.advancedsciencenews.com

www.advintellsyst.com

**Figure 5.** 1D1R crossbar array based on low-temperature-processed SiO<sub>x</sub>. a) Schematic illustration and photograph of the 1D1R SiO<sub>x</sub> memory device. The zoom-in schematic shows the device structure of one memory cell including Ti/TiO<sub>2</sub>/SiO<sub>x</sub>/Pt. b) SEM images showing the top-view and cross-sectional view of the fabricated 1D1R device. c) The representative *I*–V curves of the fabricated 1D1R device. d) Endurance performance of the fabricated 1D1R device. The set, reset, and read voltages are 8, 15, and 2 V, respectively. Reproduced with permission.<sup>[134]</sup> Copyright 2018, Wiley-VCH. e) Illustration of large-scale industrial crossbar arrays. Cross-sectional SEM view of 28 nm TaON-based cross-point 3D via RRAM and the zoom-in TEM image of a 3D via RRAM (30 nm × 30 nm) in (e) with a stacked TaO<sub>x</sub> diode in 28 nm Cu single damascene process. Reproduced with permission.<sup>[136]</sup> Copyright 2013, IEEE.

bipolar memristors is generally better and more reliable compared with unipolar memristors.<sup>[142,143]</sup> Another factor is that the diode cannot provide self-compliance without a complicated device structure, like the structure of Ni/AlO<sub>y</sub>/n+-Si-TiN/HfO<sub>x</sub>/ Ni reported by Liu et al.<sup>[144]</sup>

Thus, the development of high-density-integrated 1D1R is greatly limited. Li et al. reported that the integrated structure of Ni/TiO<sub>x</sub>/Ti diode and Pt/HfO<sub>2</sub>/Cu bipolar RRAM cell could demonstrate a self-compliance bipolar resistive switching behavior to suppress the undesired sneak current in a crossbar array,<sup>[145]</sup> which paves the way to designing a highly integrated 1D1R crossbar array with the elimination of inherent obstacles of 1D1R. Thus, designing diodes with high forward current density, high self-rectifying ratio, low-temperature fabrication, and easy integration with memory cell would be the key parameters that should be considered further.

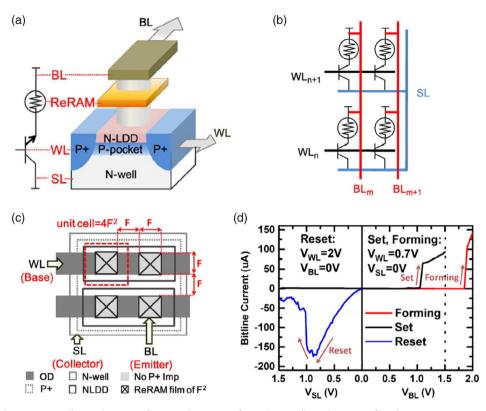

#### 3.4. 1BJT1R Cell and Crossbar Array

BJT has been widely reported as the selecting devices for PCM crossbar arrays. Seravalli and Villa et al. demonstrated a 1 Gb PCM test chip based on 1BJT1R crossbar arrays. The chip is manufactured using a 45 nm process of Humonyx. Each cell has a vertical PNP–BJT selector and a  $Ge_2Sb_2Te_5$  PCM cell. The chip offers a 266 Mb s<sup>-1</sup> read throughput and a 9 Mb s<sup>-1</sup> write throughput.<sup>[146,147]</sup> For the RRAM, due to the limitations of CMOS processes and planer structures of transistors, it is difficult to utilize the metal–oxide–semiconductor field-effect transistors (MOSFETs) to satisfy all requirements of low-voltage operations, high scalability, and large current drivability with one single cell. Hua et al. reported a new logic-compatible BJT with a vertically formed stack underneath the resistive stacked film of TiN/Ti/HfO<sub>2</sub>/TiN as a high-performance current

**ADVANCED** SCIENCE NEWS \_\_ www.advancedsciencenews.com

www.advintellsyst.com

**Figure 6.** 3D vertical BJT RRAM cell. a) Schematic of a vertical NPN BJT formed vertically under RRAM film. b) 3D RRAM array arrangement with BJT structure. c) The layout of the memory cell with vertical NPN BJT in 3D RRAM structure. d) DC curves of 3D RRAM for set/reset and forming operations. Reproduced with permission.<sup>[148]</sup> Copyright 2010, IEEE.

driver and bit-cell selector, as shown in **Figure 6**a.<sup>[148]</sup> The corresponding 3D RRAM array arrangement with BJT structure is shown in Figure 6b. The shallow and tiny n-type lightly doped domain (NLDD) acts as the bit line in connection with the RRAM film and the very thin and self-aligned p-pocket implant works as the word line (Figure 6c). Such a new 3D RRAM cell could be easily implemented in advanced CMOS logic platforms for the ultrahigh-density and very-low-voltage non-volatile memory (NVM) applications due to its area-saving device structure and efficient operation driven by the high-gain BJT with a low voltage of 2V for reset and 1.5V for the set processes (Figure 6d).

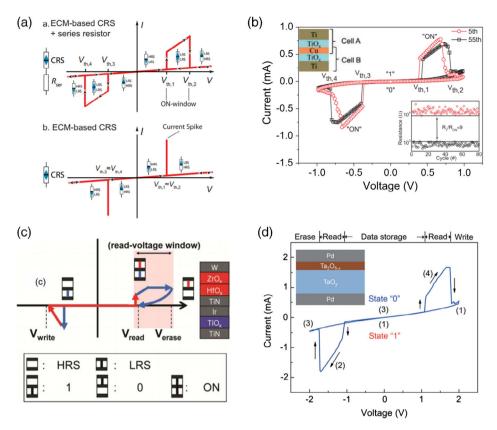

#### 3.5. CRS Memory Cell and Crossbar Array

CRS provides another way to avoid sneak-path current without extra access elements, at the cost of duplicating the number of memristors. Each CRS cell usually has two antiserially connected bipolar memristors in a back-to-back way.<sup>[149–152]</sup> As they share a common electrode, when one of the memristors is programmed into LRS, the other will be programmed into a high-resistance state (HRS).<sup>[149]</sup> To achieve the stability on a window, a series resistor is normally required for entertaining an asymmetry for the set and reset device voltages, making a level read operation possible, as shown in **Figure 7a**.<sup>[150]</sup> So far, most CRS cells reported previously could be classified into two groups: 1) CRS using two symmetric memory cells. Lee et al. exhibited a CRS cell

in the oxide-based RRAM device based on the inverse materials order  $(Pt/ZrO_x/HfO_x/metal/HfO_x/ZrO_x/Pt)$  of two symmetric memory cells,<sup>[153]</sup> where the oxygen ion motion between the ZrOx and HfOx oxides contributed to resistive switching. Wang et al. reported a CRS device consisting of two symmetric memory cells based on Ti/TiO<sub>x</sub>/Cu/TiO<sub>x</sub>/Ti structure, as shown in Figure 7b.<sup>[154]</sup> Other reports of symmetrically connected pair of memory cells have been demonstrated, like Pt/BTO/LSMO/ BTO/Pt,<sup>[155]</sup> Au/a-C/CNT/a-C/Au,<sup>[156]</sup> Pt/TiO<sub>x</sub>/TiO<sub>v</sub>/TiO<sub>x</sub>/ Pt.<sup>[157]</sup> 2) CRS using two asymmetric memory cells. As the former one with two same memory cells connected usually have the fixed operation voltages and thus limited operation voltage windows, Lee et al. demonstrated a CRS cell with a structure of W/ZrOx/HfOx/TiN connected with TiN/Ir/TiOx/TiN, consisting of two asymmetric memory cells, as shown in Figure 7c.<sup>[158]</sup> The set/reset switching is positive/negative for HfOx-based memory cell, which is opposite to the switching of  $TiO_x$ -based memory device. Both of them show larger reset voltage than the set voltage, and a wide voltage-operating window in the positive-bias region has been achieved from the superimposed I-Vfeature of two merged cells. Similar results have been observed in Al/Al<sub>2</sub>O<sub>3</sub>/Au/GO/ITO<sup>[159]</sup> and ITO/GO/graphene/GO/Al.<sup>[152]</sup>

Although the CRS with two antiserially connected memory cells can effectively solve the sneak-path current, the integration complexity due to extra fabrication steps, rapid degradation of the common active internal electrode, etc. prohibits the implementation of large-scale CRS crossbar memory. A potential solution www.advancedsciencenews.com

www.advintellsvst.com

**Figure 7.** Nanocrossbar memory array with CRS structures to avoid the sneak current. a) Top panel: ECM-based CRS device connected serially with a resistor. Bottom panel: ECM-based CRS device without the series resistor. Reproduced with permission.<sup>[150]</sup> Copyright 2013, Nature Publishing Group. b) *I–V* curves of the symmetry-connected cells with the structure of Ti/TiO<sub>x</sub>/Cu/TiO<sub>x</sub>/Ti. Reproduced with permission.<sup>[154]</sup> Copyright 2016, IOP Publishing. The left top inset shows the schematic of the CRS device and the right lower inset shows the endurance performance of the CRS device at 0.5 V. c) A simple scheme of heterodevice CRS device having these two RRAMs and simple illustrations of device states. Reproduced with permission.<sup>[158]</sup> Copyright 2012, IEEE. d) The device structure of the Pd/Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>y</sub>/Pd memory devices, and the *I–V* curve of Pd/Ta<sub>2</sub>O<sub>5-x</sub>/3%-TaO<sub>y</sub>/Pd device showing bipolar resistive switching. The inset shows the same *I–V* curve on a logarithmic scale. Reproduced with permission.<sup>[161]</sup> Copyright 2012, AIP Publishing.

is a truly single memristor instead of two that can exhibit CRS. Nardi et al. proposed a CRS device based on a single memory device with the structure of TiN/HfO<sub>x</sub>/TiN.<sup>[160]</sup> However, CRS could only be observed with a uniform Hf concentration profile within the HfOx active layer.<sup>[160]</sup> Yang et al. have reported the CRS in Pd/Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>y</sub>/Pd memory cells with two designed different stoichiometric TaO<sub>x</sub> layers: an oxygen-rich layer and an oxygen-deficient layer, and the exchange of oxygen vacancies between two layers with the gradient of oxygen composition plays a vital role in the implementation of CRS (Figure 7d).<sup>[161]</sup> Similar structures have also been reported in Au/BaTiO<sub>3</sub>/NiO/Pt,<sup>[162]</sup> W/Nb<sub>2</sub>O<sub>5-x</sub>/NbO<sub>y</sub>/Pt,<sup>[163]</sup> Al/GO/ITO,<sup>[164]</sup> IrO<sub>x</sub>/GdO<sub>x</sub>/Al<sub>2</sub>O<sub>3</sub>/TiN,<sup>[165]</sup> Pt/HfAlO<sub>x</sub>/TiN,<sup>[166]</sup> Pt/HfO<sub>x</sub>/TiN,<sup>[167]</sup> and Pt/TiO<sub>2-x</sub>/TiN<sub>x</sub>O<sub>y</sub>/TiN,<sup>[168]</sup> etc.

Although there are many preliminary works on different CRS cells, several issues should be addressed before developing a high-density CRS RRAM array. In CRS, the read operation for one of the HRS involves a set transition, which requires a solution to limit the high programming current. Although the proper operation of a CRS crossbar memory array could be ensured by connecting each memory cell in series to a

selector/transistor,<sup>[138,169–172]</sup> that defeated the motivation of CRS that is selector free. A typical approach is to embed a "series resistor" into the CRS memory cell, which would limit the increase in current with the formation of a conducting filament in the switching layer.<sup>[173–176]</sup> Tappertzhofen et al. reported a novel method to realize a nondestructive readout based on a CRS cell consisting of two memory cells with similar switching properties and distinguishably different capacities.<sup>[177]</sup> Another issue is the narrow read voltage window of CRS. To our best knowledge, most of the reported RRAM devices with CRS characteristics generally exhibit a narrow read margin ( $\approx 0.5$  V), like Pt/SiO<sub>2</sub>/GeSe/Cu/SiO<sub>2</sub>/Pt,<sup>[178]</sup> Pd/Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>y</sub>/Pd,<sup>[161]</sup> W/Nb<sub>2</sub>O<sub>5-x</sub>/NbO<sub>y</sub>/Pt, and<sup>[163]</sup> TiN/HfO<sub>x</sub>/TiN.<sup>[160]</sup> Pt/ZrO<sub>x</sub>/HfO<sub>x</sub>/TiN/HFO<sub>x</sub>/ZrO<sub>x</sub>/TiN<sup>[153]</sup> and W/ZrO<sub>x</sub>/HfO<sub>x</sub>/

Pt/ZrO<sub>x</sub>/HfO<sub>x</sub>/TiN/HfO<sub>x</sub>/ZrO<sub>x</sub>/TiN<sup>[153]</sup> and W/ZrO<sub>x</sub>/HfO<sub>x</sub>/ TiN/Ir/ZrO<sub>x</sub>/TiN.<sup>[158]</sup> To address this limitation, Zhang et al. proposed a new approach with ITO/HfOx/TiN memristor to enlarge the difference between the set and reset voltages, relying on the inherent asymmetry in the O-ion exchange processes between interfaces because of the different reactivities of metal electrodes.<sup>[179]</sup> This work solves the key challenge of demonstrating array-level CRS.

#### 3.6. SRC and Crossbar Array

The aforementioned solutions to alleviate the sneak-path current issue using an additional selector, diode, or transistor would increase the complexity of the fabrication process and the cost, increase the read/write voltage, degrade the stability of memory, as well affect the scaling limitation because of the complicated device structures. Self-rectifying resistive memory could avoid the issues addressed earlier without extra rectifying devices.

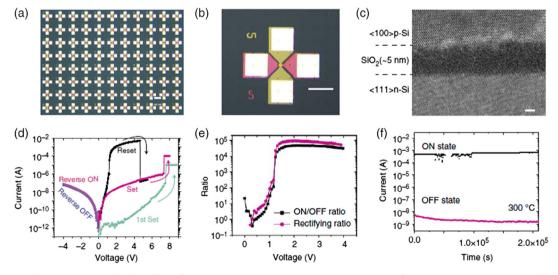

The typical structure of a self-rectifying RRAM is metalinsulator-insulator-metal (MIIM) or MIM. The large work function difference between the top and bottom electrodes is essential for the asymmetric effective barrier seen in the top and bottom electrodes to enable the rectifying feature. So far, the self-rectifying memory devices with such bilayer device structures have been intensively studied, for example, NiSi/HfO<sub>r</sub>/ TiN,<sup>[180]</sup> Ge/HfO<sub>x</sub>/Ni,<sup>[181]</sup> He-LiNbO<sub>3</sub>/Pt/SiO<sub>2</sub>/LiNbO<sub>3</sub>,<sup>[182]</sup> Pt/  $Ta_2O_5/HfO_{2-x}/TiN$ ,<sup>[183]</sup> Ni/HfO\_2/SiO\_2/Si diode,<sup>[184]</sup> Pt/TaO<sub>x</sub>/  $n-Si,^{[185]}$  Al/MoO<sub>x</sub>/Pt,<sup>[186]</sup> (ITO)/InGaZnO/ITO,<sup>[187]</sup> Pt/ HfO<sub>2-x</sub>/TiN,<sup>[188]</sup> Pt/amorphous In-Ga-Zn-O (a-IGZO)/  $TaO_x/Al_2O_3/W$ ,<sup>[189]</sup>  $Ti/SiO_xN_v/AIN/Pt$ ,<sup>[190]</sup>  $Pd/HfO_2/WO_x/$ W,<sup>[191]</sup> Ag/a-Si/p<sup>+</sup>-Si,<sup>[192]</sup> Au/ZrO<sub>2</sub>:nc-Au/n<sup>+</sup>Si,<sup>[193]</sup> Au/ Li–ZnO/ZnO/Pt,<sup>[194]</sup> Ni/SiN/HfO<sub>2</sub>/Si,<sup>[195]</sup> Pd/HfO<sub>2</sub>/TaO<sub>x</sub>/ Ta,<sup>[196]</sup> Ni/Al<sub>2</sub>O<sub>3</sub>/p-Al doped GaN (p-AlGaN),<sup>[197]</sup> Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>/ Si,<sup>[198]</sup> Pt/Ta<sub>2</sub>O<sub>5</sub>/HfO<sub>2-x</sub>/Hf,<sup>[199]</sup> Ti/GaO<sub>x</sub>/NbO<sub>x</sub>/Pt,<sup>[200]</sup> Ti/ NiO<sub>\*</sub>/Al<sub>2</sub>O<sub>3</sub>/Pt,<sup>[201]</sup> etc. Li et al. reported a p-Si/SiO<sub>2</sub>/n-Si memristor. The optical images and the cross-sectional transmission electron microscope (TEM) image are shown in Figure 8a-c, and the typical nonlinear I-V curve with unipolar behavior is shown in Figure 8d. Such a novel SRC exhibits repeatable unipolar resistance switching with a rectifying ratio of 10<sup>5</sup> and on/off ratio of  $10^4$  (Figure 8e) and the retention time up to  $2 \times 10^5$ .<sup>[202]</sup>

Moreover, the authors also demonstrated the 3D crossbar array of up to five layers of 100 nm memristors using fluid-supported silicon membranes and experimentally confirmed the successful suppression of both intra- and interlayer sneak-path currents through the built-in diodes. Kim et al. reported a forming-free memristive system based on the stacked Pt/NbOx/TiOy/NbOx/ TiN with a 30 nm contact, showing a programming current as low as 10 nA and 1 pA for the set and reset switching, respectively.<sup>[203]</sup> The self-rectifying ratio is about 10<sup>5</sup>. This work revealed that the programming power can be decreased to 8.0% of power consumption of a conventional biasing scheme when the device is used in a  $1000 \times 1000$  crossbar array with the asymmetric voltage scheme (AVS), and a power consumption reduction could be decreased possibly to 0.31% of the reference value if the AVS is combined with a nonlinear selector. This kind of low-voltage operation of the memristive device is of strong potential to be used for low-power applications such as embedded memory of low voltage or power-restricted chips.

To satisfy the strict requirements of SCM, Hsu et al. reported a forming-free and self-compliance bipolar  $Ta/TaO_x/TiO_2/Ti$  RRAM cell with extremely high endurance over  $10^{12}$  cycles.<sup>[204]</sup> The self-rectification ratio achieved in this work could be up to  $10^5$  required for ultrahigh-density 3D vertical RRAM. In addition, the multiple-level-per-cell capability, room-temperature processes, and fabrication-friendly materials demonstrated in this memristive system make its potential promising to realize high-density and high-performance SCM.

Normally, the growth of bilayer dielectric structure increases the cost and complexity of manufacturing. Therefore, lowtemperature compatible processes should be developed. Oh et al. reported a forming-free and self-compliance resistive switching device based on Au/Ni/FeO<sub>x</sub>-GO/Si<sub>3</sub>N<sub>4</sub>/n<sup>+</sup>-Si

**Figure 8.** 3D crossbar array integrated with self-rectifying Si/SiO<sub>2</sub>/Si memristors. a) Top-view picture of an  $11 \times 8$  memristor array with high fabrication yield of a single cross-point device. Scale bar: 100 µm. b) The zoom-in picture of a single device shown in (a), with 5 µm × 5 µm cross-point device. Scale bar: 50 µm. c) Cross-sectional TEM image of the device with vertically stacked Si/SiO<sub>2</sub>/Si layers, clearly showing the crystalline structure of the top and bottom Si layers and the 5 nm SiO<sub>2</sub> as the middle amorphous layer. Scale bar: 2 nm. d) The representative unipolar *I–V* resistive switching curves. The top p-Si layer was applied with bias voltage and the bottom n-Si layer was grounded. The set and reset voltages are 7.5 and 4.5 V, respectively. The turquoise curve is the first setting voltage with almost the same voltage, indicating the formatting-free feature of the device. e) The bias voltage-dependent on/off ratio conductance ratio and the rectifying ratio. f) Retention behaviors test at room temperature. The conductance states could be maintained for more than  $2 \times 10^5$  s. Reproduced with permission.<sup>[204]</sup> Copyright 2017, Nature Publishing Group.

structure with an excellent resistive switching ratio (greater than 10<sup>4</sup>) and a rectification ratio higher than  $10^{4}$ .<sup>[205]</sup> The solution-processed FeO<sub>x</sub>-GO active layer showed comparable performance with those devices fabricated using vacuum deposition processes, making possible the lower fabrication cost of self-rectifying memory devices.

Although the typical bilayer dielectric layer structure has been investigated successfully for developing self-rectifying resistive switching, developing a single material with concurrent high-performance switching and self-rectification would decrease the fabrication complicity and increase the integration level. Recently, Yao et al. reported a RRAM device based on a chiral metal–organic framework (MOF) FJU-23-H<sub>2</sub>O with switched hydrogen bond pathway within its channels, exhibiting an ultralow set voltage ( $\approx 0.2$  V), a high ON/OFF ratio ( $\approx 10^5$ ), and a high rectification ratio ( $\approx 10^5$ ).<sup>[206]</sup> Its resistive switching behavior originated from the turn on/off of the switched hydrogen bond pathway under the stimulus of DC voltages. This work is not only the first MOF with voltage-gated proton conduction but also the first single material showing both rectifying and resistive switching effects.

#### 3.7. SSC and Crossbar Array

To date, most solutions like 1S1R, 1D1R, 1T1R, SRC, and CRS are achieved by connecting two MIM cells in series. Each solution has its unique advantage that cannot be combined with that of alternative solutions, thus unable to completely resolve the sneak-path current issue. For example, 1) the 1S1R AND 1D1R cell cannot be integrated with a high capacity due to complex fabrication (including etching issue), 2) the SRC cannot provide sufficiently low sneak currents, which are essential for large integration, and 3) the CRS cell exhibits destructive read operation and high sneak currents due to its intrinsic device structure.<sup>[48]</sup> All the former solutions are stuck at an integration capacity of megabit (10<sup>6</sup> bits). Indeed, a conceptually new memory cell has to be developed.

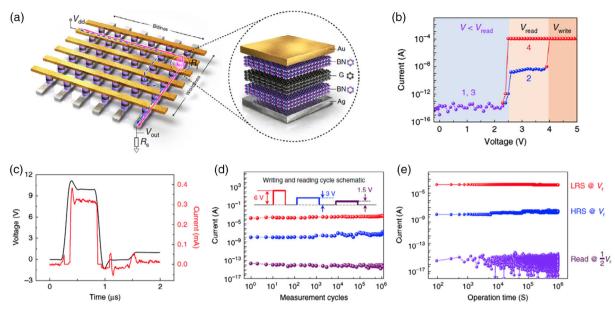

The concept of self-selective resistive switching in a single cell offers a new strategy to overcome the sneak-path current issue of a memory device in the crossbar array structure without additional stacking of active devices. By integrating two oxide layers as an insulating layer, it exhibits a selective functionality with an engineered nonlinearity. Other candidates like vanadium oxide  $(VO_x)$ ,<sup>[207]</sup> with self-selecting resistive switching performance for crossbar memory array was demonstrated by Myungwoo et al. due to the first-order MIT property. The nanoscale VO<sub>x</sub> device exhibited self-selective switching and memory switching after electroforming. Ma et al. reported other self-selective resistive switching memory cells with a thermal-oxidized HfO<sub>x</sub> layer in combination with a sputtered Ta<sub>2</sub>O<sub>5</sub> layer configured as an active stack.<sup>[208]</sup> which represents high-on-state half-bias nonlinearity of  $\approx$ 650, a sub-µA operating current, and high on/off ratios above 100×. Kwon et al. reported a selector-less memristor for high uniformity and low power consumption using the structurally engineered nanoporous Ta<sub>2</sub>O<sub>5-x</sub> and achieved ultralow power consumption ( $\approx 2.7 \times 10^{-6}$  W).<sup>[209]</sup> Wang et al. utilized a  $VO_2/TaO_x$  bilayer structure to realize the volatile threshold switching and multilevel nonvolatile resistive switching and applied such hybrid self-selective switching to the selfactivation neural network.<sup>[210]</sup> Xu et al. reported a  $TiN/TiO_x/$ HfO<sub>2</sub>/Ru self-selective device formed by a self-aligned technique, with the off-state leakage current as low as 0.1 pA and operating current below 1 µA.<sup>[211]</sup> The LRS exhibits high nonlinearity  $(10^3)$ . The programming and erasing speeds are 100 and 400 ns, respectively, and the excellent endurance shows  $10^7$ cycles. A  $4 \times 8 \times 32$  3D vertical RRAM array was further demonstrated with a sufficient read margin up to 10 Mb. Eight-layer 3D vertical RRAM with excellent scalability toward SCM was reported by Luo et al. from the same group.<sup>[212]</sup> This work successfully extended the SSC design into the eight-layer 3D array and explored the scaling limit of this architecture of 5 nm cell size and 4 nm pitch in the vertical dimension demonstrated experimentally. Recently, Sun et al. realized fast and energyefficient 2D self-selective memory cells using a high-quality van der Waals heterostructure of h-BN and graphene, as shown in Figure 9a, which is compatible with an integrated capacity of  $10^{12}$ .<sup>[48]</sup> A current of 10 fA at a low voltage bias (<3 V) and abruptly a current of 10 mA at a high voltage bias in a stable memory device was achieved (Figure 9b). The atomically sharp and chemically inert interface between the h-BN and graphene layers created a rapid reading/writing process with a time constant of tens of nanoseconds (rising time:  $\approx$ 50 ns and falling time:  $\approx$ 15 ns), as shown in Figure 9c, outperforming the current flash memory technology. The origin of such a memristive behavior is that Ag ions migrate through the h-BN layer during the memory operation and their further migration is blocked by the strongly bonded graphene; then, the boron vacancies contribute to the conductive path in another h-BN layer with the continuously increased voltage.<sup>[48]</sup> The endurance and retention behaviors of the involved three resistance states are shown in Figure 9d,e up to 10<sup>6</sup> switching cycles and 10<sup>6</sup> s, respectively. Such a new conceptual memory device based on a novel 2D heterostructure will open up a new research field, lowdimensional nanomaterials-based memory and neuromorphic computing.

#### 3.8. Comparison of Various Architectures

In this part, we compare the strengths and weakness of each architecture. 1) For the 1T1R architecture, it is compatible with basic operations for in-memory logic, machine learning, and neuromorphic computing, featuring mature process flow derived from DRAM technology. However, it has a relatively small device areal density due to the large footprint of planar FETs, and the device density is further limited by the difficulty to integrate 1T1Rs in 3D. 2) For the 1BJT1R architecture, it is compatible with basic operations for in-memory logic, machine learning, and neuromorphic computing, which has a smaller footprint compared with planar FETs with the use of vertical BJTs and a lower fabrication cost compared with FETs. However, BJT selectors are of lower input impedance and current gain compared with FET selectors and tend to show lower switching frequency compared with FET selectors. 3) For CRS architecture, it features large device areal density when it is integrated in 3D, which is also compatible with operations for in-memory logic. However, CRS reading may be destructive, incurring extra rewriting energy, and suffer from integration www.advancedsciencenews.com

www.advintellsyst.com

**Figure 9.** Self-selective crossbar memory array based on van der Waals heterostructures. a) Schematic figure of the van der Waals heterostructure integrated with crossbar memory array architecture. b) *I–V* curve of a typical memory cell in the memristor array. The four numbers represent four different resistance states of the memory cell. The selectivity of this one-body self-selective memory cell is  $10^{10}$ , and the memory window is around  $10^4$ . The Au electrode was kept in connection with the ground. c) The switching speed of the self-selective memory cell is about tens of nanoseconds. d) Endurance of switching behavior of the involved three resistance states, with voltage pulse trains of  $10^6$  measurement cycles. e) Retention behaviors of the three resistance states at a time of  $10^6$  s. Reproduced with permission.<sup>[48]</sup> Copyright 2019, Nature Publishing Group.

complexity due to extra fabrication steps. It is also vulnerable to the rapid degradation of the common active internal electrode. 4) For SSC and 1D1R architecture, both of them feature large device areal density when they are integrated in 3D. In addition, 1D1R-based storage has been commercialized by Intel and Micron, branded as Optane memory. However, both SSC and 1D1R are less compatible with basic operations for inmemory logic, machine learning, and neuromorphic computing. 5) For SSC and 1S1R architecture, they feature large device areal density when they are integrated in 3D. Their bidirectional nonlinearity in their I-V characteristics allows them to work with bipolar memristors but faces the same issue similar to SSC and 1D1R.

To clearly compare the performances of the discussed architectures in this Review, we summarize with key parameters like on current, on/off ratio,  $V_{set}/V_{reset}$ , polarity, operation temperature, retention, and endurance in **Table 1**.

#### 4. Impact of Wire Resistance

In large crossbar arrays, the current passing through the metal wires would lead to significant voltage degradation, decreasing the voltage drop on the farthest cell in the crossbar array, and this finally results in write failure, which is also known as the "IR drop" issue. Such resistance affects both memory readout margin and the precision of vector-matrix multiplications. The latter poses a technical challenge to applications such as machine learning and signal processing in the analog domain.

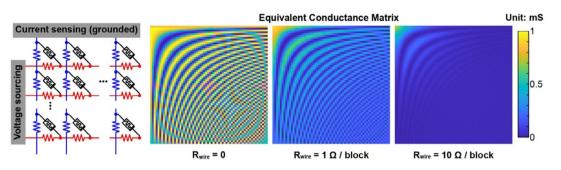

To illustrate the impact of the wire resistance, Hu et al. use the mapping of a discrete cosine transformation matrix as an example and assume that the  $64 \times 64$  discrete cosine transformation matrix is linearly mapped to the conductance of a memristor array in the range [0, 1 mS].<sup>[213]</sup> In case that there is no wire resistance, the voltages are constants along red row electrodes and blue column electrodes. The transformation from the forced

| Types  | On current [A]    | On/Off ratio                     | Operation polarity | Operation temperature [K] | Retention [s]        | Endurance            | Refs  |

|--------|-------------------|----------------------------------|--------------------|---------------------------|----------------------|----------------------|-------|

| 1S1R   | $5 	imes 10^{-4}$ | 10 <sup>9</sup>                  | Biploar            | —                         | _                    | 10 <sup>6</sup>      | [52]  |

| 1T1R   | 10 <sup>-3</sup>  | 10 <sup>8</sup>                  | Unipolar           | 300                       | 10 <sup>5</sup>      | 10 <sup>8</sup>      | [108] |

| 1D1R   | $pprox 10^{-4}$   | 10 <sup>8</sup>                  | Unipolar           | 473                       | ≈10⁵                 | 10 <sup>4</sup>      | [112] |

| 1BJR1T | ≈10 <sup>-5</sup> | ≈10                              | Unipolar           | _                         | 10 <sup>3</sup>      | 10 <sup>5</sup>      | [148] |

| CRS    | 10 <sup>-2</sup>  | 10 <sup>2</sup> -10 <sup>3</sup> | Biploar            | ≈360                      | 10 <sup>4</sup>      | $pprox 2 	imes 10^2$ | [152] |

| SRC    | 10 <sup>-4</sup>  | $\approx 10^4$                   | Unipolar           | 573                       | $pprox 2 	imes 10^5$ | $\approx 10^2$       | [202] |

| SSC    | 10 <sup>-4</sup>  | 10 <sup>10</sup>                 | Biploar            | 450                       | 10 <sup>6</sup>      | 10 <sup>6</sup>      | [48]  |

Table 1. Comparison of key parameters and functions among different device structures.

Figure 10. The equivalent circuit of a memristor crossbar array with parasitic wire resistance. The color maps illustrate the effective conductance matrix  $G_{\text{eff}}$  that gradually deviates from the targeting conductance matrix  $G_{\text{target}}$  (discrete cosine transformation matrix mapped to [0, 1 mS] with increasing wire resistance.

input voltage vector  $\vec{V}$  to the sensed output current vector  $\overrightarrow{I_{target}}$  is governed by the vector-matrix multiplication  $\overrightarrow{I_{target}} = G_{target}\vec{V}$ where  $G_{target}$  is the conductance matrix of the memristor array. In case the electrodes are of nonzero resistance, such as 1  $\Omega$ / block, the currents flowing through the electrodes produce voltage drops. As a result, the memristor that is far from the voltage sourcing and/or current-sensing edge receives reduced bias. The effect of the wire resistance can be absorbed by  $\overrightarrow{I_{eff}} = G_{eff}\vec{V}$ , where  $G_{eff}$  is the effective conductance matrix that is clearly different from  $G_{target}$ , as shown in **Figure 10**, particularly the memristors far from the voltage sourcing and/or current-sensing edge. In addition, as shown in Figure 10, the increase in the wire resistance, for example, to 10  $\Omega$ /block, will lead to a larger deviation between  $G_{eff}$  and  $G_{target}$ , which further degrades the precision of the vector-matrix multiplication.

The wire resistance impact can be tackled by engineering the conductance range of the memristors. For example, a large ratio between the wire and memristor conductance can reduce the voltage drops across the wires. In addition, circuit and algorithm-level techniques have been invented to mitigate the impact of the wire resistance for machine learning. Hu et al. proposed a conversion method to compute the actual memristor crossbar conductance matrix that can approximate a targeting conductance matrix, based on numerically solving the Kirchhoff equations.<sup>[213]</sup> In addition, Jeong et al. developed a compact analytic compensation scheme that rescales each element of the sensed current vector by a constant. The scheme

is based on the observation that the majority of the current deviation can be accounted by a model assuming constant input voltage and conductance.<sup>[214]</sup> Liao et al. demonstrated diagonal matrix regression, where two diagonal matrices approximate the impact of row and column wire resistance, which can balance the computational complexity and the accuracy of vector-matrix multiplication.<sup>[215]</sup> There are some other circuit techniques to deal with the voltage drop issue, by adding write drivers at both sides of bitlines, as written by Zhang et al.<sup>[216]</sup>

www.advintellsvst.com

Another factor is that the crossbar line capacitance could add both read/write delay time and extra current sneak paths,<sup>[48,217–219]</sup> which will further degrade the performance of the memory array. Thus, in real application with consideration of line resistance, the position of the selected cell will have a significant influence on the voltage margin.

## 5. Applications in Machine Learning and Neuromorphic Computing

In addition to storage class and embedded memory, 1R- and 1T1R-type resistive memory crossbars are frequently applied to machine learning and neuromorphic computing.

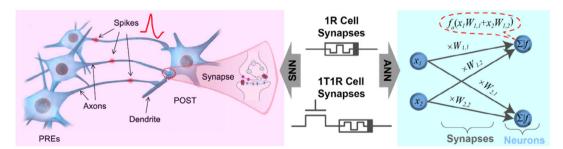

So far, 1R and 1T1R crossbars have been used for machine learning by hardware implementation of ANNs. In addition, they are also used in neuromorphic computing or the SNNs which mimic how our brain works. As schematically shown in **Figure 11**, the SNN is a bioinspired neural network, consisting of two types of building blocks, the neurons and the synapses.

**Figure 11.** Illustration of 1R and 1T1R cells for being used as synapses in both SNNs and artificial neural networks (ANNs). In an SNN, the neurons communicate in spikes, which are modulated by synapses interfacing neurons. The neuron integrates incoming spikes and fires its own spike if the stimulation exceeds a threshold. In an ANN, the neurons and synapses are abstracted to nodes and arrows of computational graphs, representing weighted summation followed by activation and scalar(scalar multiplication, respectively. Reproduced with permission.<sup>[40]</sup> Copyright 2018, AAAS.

The latter are junctions interfacing two neurons, which can modulate the signal transmission strength between neurons, forming the basis of our memory. Each neuron accumulates incoming spikes from upper-stream neurons through synapses. Once the stimulation exceeds a threshold, the neuron fires its own spike or action potential that propagates along its axon to reach the downstream neurons. Resistive 1 R and 1T1R cells have been widely reported for their potential to serve as compact hardware synapses, by mapping the signal transmission strength to their conductance.<sup>[12,13,220–230]</sup> In addition, chemical synapses own the capability to change connection strength depending on the historic signal that has transmitted through them. This could be replicated using ionic or electronic switching dynamics of 1 R or 1T1R resistive memory cells, which exhibit various short- and long-term synaptic plasticities. Such plasticity is the foundation of the learning capability of biocreatures. In contrast, ANN is an abstraction of SNN, essentially a computational graph where arrows usually represent scalar-scalar multiplications, whereas nodes stand for summation followed by nonlinear activation functions. (see the left panel of Figure 11) The cascaded

nonlinear transformations endow ANNs with the capability to approximate arbitrary functions, provided the size and depth of the network are sufficiently large.<sup>[231]</sup> Likely in SNNs the 1R and 1T1R cells can serve as the synapses in ANNs. As the current flowing through a 1R or 1T1R is governed by Ohm's law, the multiplication of its conductance and voltage can be naturally mapped to the multiplication of the synaptic weight and the value of the upper-stream node. In addition, the summation can be automatically fulfilled by Kirchhoff's current law in crossbars, as will be discussed in the next paragraph.

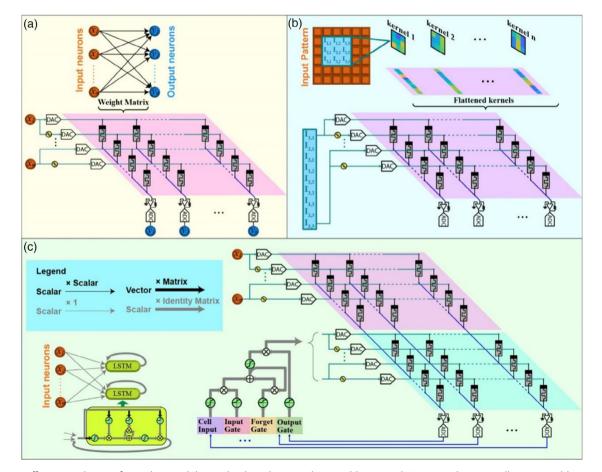

Either an SNN or ANN usually consists of a stack of assorted layers. Typical layer topologies that 1R and 1T1R crossbars have implemented comprise a fully connected layer, convolutional layer, and recurrent layer. As shown in **Figure 12**a, in a fully connected layer, each input neuron (node) is connected to all output neurons. Therefore,  $\vec{y} = W\vec{x}$ , where  $\vec{x}$  and  $\vec{y}$  are the vectors of input and output neurons, respectively. For simplicity, bias and activation are ignored here. W denotes the weights of all the black arrows in the form of a matrix, for example,  $W_{i,j}$  stands for the connection strength between the i-th input neuron and

**Figure 12.** Different topologies of neural network layers that have been implemented by 1 R and 1T1R crossbars. a) Fully connected layer. In a fully connected layer, each input neuron connects to all output neurons. The output neuron vector is the multiplication between the input neuron vector and the weight matrix which can be mapped to the conductance of a 1R or 1T1R crossbar. b) Convolutional layer. An input image is scanned by a convolution window. The pixels within the window are element-wise multiplied with a set of kernels before accumulation. The flattened kernels can be mapped to the conductance of a 1R or 1T1R crossbar. c) Recurrent layer. Here an example of a long short-term memory (LSTM) layer is used. An LSTM node has its internal state that is updated by four gates. The vector-matrix multiplications of LSTM nodes can be physically implemented by two 1R or 1T1R subarrays, one for the external input and the other one for recurrent input.

j-th output neuron. Therefore, the weight matrix W can be conveniently mapped to the conductance matrix of a 1R or 1T1R crossbar. By doing so, the vector-matrix multiplication (or weighted summation) will be physically carried out by Ohm's law for multiplication and Kirchhoff's current law for summation in one computational cycle, regardless of the dimension of the matrix. This may offer a large throughput and efficiency boost over conventional digital systems, as the data are both stored and processed on the same resistive memory element, which avoids the frequent data shuttling between physically separated memory and processing units in conventional digital hardware that incurs large latency and energy consumption.<sup>[1,28,232-238]</sup> In addition to the fully connected layer, a convolutional layer is shown in Figure 12b, which is mostly famous for its applications in computer vision. The input such as a 2D image will be scanned by a convolution window that is outlined by the green box. The subarray of the input falling to the window will be multiplied element wise with a set of kernels, followed by kernel-wise summation, which completes a stride of the convolution. As flattened kernels can be concatenated as a matrix and mapped to the conductance of a 1R or 1T1R crossbar, such a convolutional stride again becomes a vector-matrix multiplication that can be physically accelerated by crossbars like a fully connected layer. Moreover, Figure 12c shows an LSTM layer, a widely used recurrent layer with nodes that connect to themselves via feedback loops. Such looped connections make a recurrent layer a dynamic system, which has an internal state, which can remember the historic inputs, with wide applications in temporal information processing. Here, each LSTM node consists of four gates, which adds and removes information from its internal state at each time step. The vector-matrix multiplication involved in LSTM can be conveniently mapped to a 1R or 1T1R crossbar with two subarrays. One of the subarrays is multiplied with an external input vector at each time step, whereas the other subarray handles the recurrent input that depends on the output of the crossbar at the last time point.

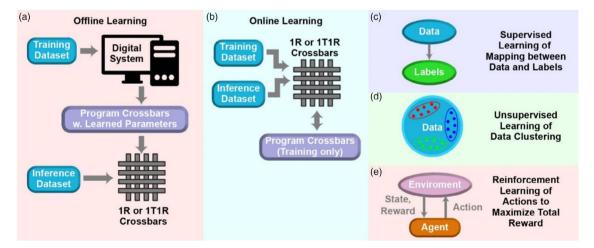

The associated learning of the 1R and 1T1R crossbars can be offline, online, or a hybrid. As shown in Figure 13a, in the process of offline learning, the parameters/weights of a neural network are first learnt on an alternative computing system, such as a digital computer, before being converted to the conductance of 1Rs or 1T1Rs and physically programmed into the crossbars. The crossbar will then be able to work with unseen data or the inference dataset. This approach features the least frequent programming of 1R or 1T1R crossbars, but it has difficulty adapting to the hardware nonidealities, such as bad devices of the crossbar, and is unable to undertake learning in real time. As shown in Figure 13b, online learning refers to the process where the conductance of 1R and 1T1R crossbars is updated during the course of learning, which is considerably challenging as there are concurrent requirements on the programming linearity, precision, energy, and speed.

The learning can also be classified according to the available information. For example, as shown in Figure 13c, the learning can be supervised with example input-output pairs, and the neural network will be able to learn a mapping between the input and output. In case the input data is not labeled, as shown in Figure 13d, the learning can be unsupervised, which understands the internal structure of the dataset that is frequently used to cluster data. Figure 13e shows the scenario of reinforcement learning, where a learning agent interacts with an unknown environment. The agent receives some information about the environment (so-called state) and a reward signal at each time point. The agent learns the strategy to apply an action to the environment to maximize the accumulated reward signal. Such learning has triumphed over human players in games that were believed humans would long dominate.<sup>[239,240]</sup>

**Figure 13.** Different types of learnings that have been implemented on 1R or 1T1R crossbars. a,b) In terms of where the neural network parameters are optimized, the learning can be offline, as shown in (a). The optimization is done on a digital platform before converting the parameters to conductance and crossbar programming. In contrast, the learning can be online, as shown in (b), where the crossbar conductance is updated along the course of learning. c–e) In terms of the available information, the learning can be supervised, given the data with paired labels, and the learning aims to find out the mapping between them. Or the learning can be unsupervised if the input data is not labeled, which discovers the structure of the data, for example, by clustering them. Or the learning can be reinforcement, where an agent interacts with an unknown environment to find out a strategy to maximize the accumulated reward.

We would like to point out that different cell structures are mainly used to mitigate the sneak-path currents in reading and programming a single device. This may be less compatible with the parallel programming operations required by logic-inmemory, such as the IMPLY<sup>[241]</sup> and MAGIC<sup>[241]</sup> protocols, as well as the parallel reading used in vector-matrix multiplications<sup>[242–244]</sup> for both machine learning and neuromorphic computing. Thus, we discuss the required performance one by one as follows for data storage applications.

IDVANCED

www.advancedsciencenews.com

ON/OFF ratio and/or Nonlinearity: The ON/OFF ratio or current–voltage nonlinearity of selecting devices dictates the storage capacity or the size of the memristor array.<sup>[245–249]</sup> An ideal selecting device would possess infinite resistance when it is unselected (e.g., biased at  $V_{half-select}$ ) and zero resistance when it is selected (e.g., biased at  $V_{select}$ ). In contrast, a small ON/OFF ratio will clearly impact both read margin during reading<sup>[249]</sup> and voltage/current delivery during programming.<sup>[247]</sup>

Retention: Threshold resistive switching selectors, such as those based on MIT,<sup>[82,250]</sup> ovonic switching,<sup>[251]</sup> and metal-filament formation/rupture,<sup>[51]</sup> feature nonzero delay of relaxing their conductance back to OFF states upon the cease of selecting signals. Therefore, the retention time affects the read/write throughput, particularly if the reading or writing is conducted in a row-by-row or column-by-column fashion. Diode and tunneling <sup>[252]</sup> selectors ideally have zero retention, although, in reality, the time to establish the proper bias will be dependent on the parasitic capacitance.

Endurance: Like retention, for those selectors based on threshold resistive switching, they usually exhibit finite endurance or a number of switching cycles before the breakdown of the permanent dielectric layer, which limits the lifespan of the underlying data storage system. Record high endurance of 10<sup>12</sup> has been demonstrated on NbO<sub>2</sub> MIT selectors.<sup>[253]</sup> Up to 10<sup>8</sup> cycles have also been observed on ovonic<sup>[251]</sup> and metal-filament formation/ rupture selectors.<sup>[51]</sup> In contrast, diodes and tunneling selectors ideally have no limit on their lifespan as no resistive switching is needed.

### 6. Example of 1R Crossbars

ANNs at UCSB: The team of Professor Dimitri Strukov is among the first in demonstrating fully connected and recurrent ANNs using RRAM 1R crossbars, which applied to both offline and online supervised learning in pattern classification and optimization. Alibart et al. reported the first single-layer fully connected ANN made of  $TiO_{2-x}$  RRAM crossbars to learn 3 × 3 binary patterns, via both offline and online supervised learning,<sup>[254]</sup> whereas a larger Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2-x</sub> RRAM crossbar was built by Prezioso et al. to classify similar patterns.<sup>[242]</sup> A two-layer fully connected network was developed by Bayat et al. to classify  $4 \times 4$  patterns with a crossbar of similar RRAMs, using offline supervised learning. The crossbar was paired with analog-hidden neurons to get rid of the tedious analog-digital conversions.<sup>[255]</sup> In addition to fully connected ANNs, a restricted Boltzmann machine, a recurrent stochastic network, has been realized on a 20  $\times$  20 RRAM 1 R crossbar by Mahmoodi et al.  $^{[256]}$  The key feature is the tunable stochasticity using external noisy current injection. As the amplitude of the injected noise can be correlated with the "thermal fluctuation" in an Ising model, a Hopfield network made of  $64 \times 64$  RRAM 1 R crossbar was used by Mahmoodi et al. to implement stochastic simulated annealing, chaotic simulated annealing, as well as exponential annealing, which shows fast convergence to the global energy minimum than the case without noise injection.<sup>[257]</sup>

ANNs at GIST: The team of Professor Byung-Geun Lee developed a RRAM 1 R crossbar made of  $Pr_{0.7}Ca_{0.3}MnO_3$  (PCMO) RRAMs in collaboration with POSTECH. Using 192 PCMO cells, Park et al. implemented a single-layer fully connected ANN to classify electroencephalography signals via offline supervised learning.<sup>[258]</sup>

ANNs and SNNs at UMich: Professor Wei Lu's group developed various RRAM 1 R crossbars that have pioneered many novel applications of ANNs and SNNs.

ANN-wise, dimensionality reduction was conducted by Choi et al. using online unsupervised learning on a TaO<sub>x</sub> RRAM 1R crossbar for principal component analysis of the breast cancer dataset.<sup>[259]</sup> A similar crossbar used by Jeong et al. was for the classification of the IRIS dataset, which implemented unsupervised K-means clustering through online learning.<sup>[260]</sup> In addition, Sheridan et al. creatively found sparse representations via a locally competitive algorithm on an offline learnt dictionary physically mapped to a  $32 \times 32$  WO<sub>x</sub> RRAM 1R crossbar.<sup>[261]</sup> Moreover, Cai et al. developed the first integrated RRAM computing system that comes with a  $108 \times 54$  RRAM 1R crossbar array with on-chip sourcing and sensing circuitry as well as a reduced instruction set computer (RISC) processor built on a 180 nm technology node.<sup>[3]</sup> Moreover, for optimization tasks, Shin et al. solved a 2D spin-glass problem by mapping the coupling matrix to TaO<sub>x</sub> RRAM crossbars. The total energy was minimized by flipping a random spin if it reduces the total energy or was decided by a stochastic Cu-based RRAM.

In terms of SNNs, a liquid-state machine, a special SNN is rooted on the concept of reservoir computing, which has been demonstrated by Du et al., Moon et al., and Zhu et al., using the short-term memory of RRAM. Such systems have revealed their advantages in online supervised learning of temporal sequences, with applications in spoken number recognition,<sup>[262]</sup> chaotic series prediction,<sup>[263]</sup> and neural firing pattern classification.<sup>[25]</sup>

SNNs at Southampton: The group of Professor Themis Prodromakis creatively devised a scheme to simulate synaptic plasticity using the switching dynamics of  $TiO_2$  RRAMs. Serb et al. demonstrated a simple fully connected SNN with hardware-encoded spike-timing-dependent plasticity (STDP) for online unsupervised learning of pattern clustering.<sup>[264]</sup>

ANNs from Polimi: Professor Daniele Ielmini's team implemented linear and logistic regressions for the first time with RRAM 1R crossbars. Sun et al. reported the training of both linear and logistic regressions on an RRAM 1R crossbar with feedback configuration, which can fast optimize the output layer of an ANN.<sup>[265]</sup>

### 7. Examples of 1T1R Crossbars

ANNs and SNNs from IBM: Dr. Geffory Burr, Dr. Evangelos Eleftheriou, Dr. Abu Sebastian, and their colleagues from

IBM have advanced ANNs and SNNs based on PCM 1T1R crossbars.

DVANCED

www.advancedsciencenews.com