# Bi<sub>2</sub>O<sub>2</sub>Se based MAGIC (Memristor Aided loGIC)

Bo Liu<sup>a\*</sup>, Yudi Zhao<sup>b</sup>, Dharmendra Verma<sup>c</sup>, Le An Wang<sup>a</sup>, Hanyuan Liang<sup>d</sup>, Hui Zhu<sup>a</sup>, Lain-Jong Li<sup>c,f</sup> Tuo-Hung Hou<sup>g</sup>, Chao-Sung Lai<sup>c,h,i,j\*</sup>.

- <sup>a</sup> Faculty of Information Technology, College of Microelectronics, Beijing University of Technology, Beijing, 100124,People's Republic of China

- <sup>b</sup> School of Information and Communication Engineering, Beijing Information Science &

Technology University, Beijing 100101, China

- <sup>c</sup> Department of Electronic Engineering, Chang Gung University, Guishan Dist., 33302, Taoyuan, Taiwan

- <sup>d</sup> School of Electrical Engineering and Computer Science, The Pennsylvania State University, University Park, USA

- <sup>e</sup> Physical Sciences and Engineering Division, King Abdullah University of Science and Technology, Thuwal 23955 6900, Saudi Arabia

- <sup>f</sup> Department of Mechanical Engineering, The University of Hong Kong, Pokfulam Road, Hong Kong

- <sup>g</sup> Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, 300, Taiwan

- <sup>h</sup> Biosensor Group, Biomedical Engineering Research Center, Chang Gung University, Guishan Dist.,

33302, Taoyuan, Taiwan

- <sup>i</sup> Department of Nephrology, Chang Gung Memorial Hospital, Guishan Dist., 33305, Linkou, Taiwan

- <sup>j</sup> Department of Materials Engineering, Ming Chi University of Technology, Taishan Dist., 24301, New Taipei City, Taiwan

E-mail address: boliu.ele@bjut.edu.cn and cslai@mail.cgu.edu.tw

Key words: Bi<sub>2</sub>O<sub>2</sub>Se, RRAM, CAFM, kinetic Monte Carlo, MAGIC,

### **Abstract**

Implementing two dimensional materials into memristor architecture has been a new research focus recently, taking the advantages of their atomic thickness, unique lattice, physical and electronic properties. Among the van der Waals family, Bi<sub>2</sub>O<sub>2</sub>Se is an emerging ternary two dimensional layered material with ambient stability, suitable band structure and high conductivity, which exhibits supreme potential on electronic application. In this work, we proposed and experimentally demonstrated a Bi<sub>2</sub>O<sub>2</sub>Se based MAGIC (stands for Memristor Aided logic). Via carefully tuned the electric field polarity of Bi<sub>2</sub>O<sub>2</sub>Se through Pd contact, configurable NAND gate with zero static power consumption was realized. To provide more knowledge on the NAND operation, kinetic Monte Carlo simulation has been carried out. Due to the NAND gate is a universal logic gate, cascading more NAND gates could exhibit versatile logic functions. In this scenario, the proposed Bi<sub>2</sub>O<sub>2</sub>Se based MAGIC could be a promising building block for developing next-generation in-memory logic computers with multifunction.

#### 1. Introduction

The modern computer is based on von Neumann architecture, where data shuttled back and forth between processing unit and memory unit. These physically separation represents a fundamental limitation of modern computers, known as the memory wall<sup>[1]</sup>. To alleviate this issue, methods have been proposed, e.g. cache hierarchies, advanced 2.5D and 3D packaging, and monolithic logic-memory integration, which aim at improving memory access latency, and increasing communication bandwidth between computation and memory units. spatial architectures, where distributed on chip memory is closer to the computation unit, as well as further scaling of integrated circuits (IC), enabling more transistors placed into the same chip area. However, the current Si based CMOS technology has encountered significant hardships to continue its revolutionary trajectory based on Moore's law, because of the fundamental thermodynamic limitations at the device physics level and the fundamental quantum mechanical limitations at the material level. Among those methods, Further performance enhancement would rely on novel approaches to break the von Neumann separation and the in memory computing with resistive switching devices seems to be a promising way. The resistive switching devices has aroused worldwide research interest due to its high density, industry compatible fabrication technologies, fast resistive switching and high stability between its high and low resistance states (HRS/LRS). The toggling between HRS and LRS in a resistive switching device is through forming or rupture a conductive filament in its sandwiched metal/insulation/metal (MIM) structure, which typically contains oxygen vacancies in valence change cells (VCM) or ionic metals (such as Ag or Cu) in electrochemical metallization cells (ECM)<sup>[2]</sup>. Through leveraging their conditional resistive switching properties, logic operations can be executed in multiple device architectures including one memristor-one resistor (1M1R)[3], one transistor-one RRAM (1T1R)[4], one selector-one RRAM (1S1R)<sup>[5]</sup> as well as complementary resistive switching (CRS)<sup>[6]</sup>. Based on those structures, noteworthy progress in this area have been achieved, including material implication, 16 logic operations, full adder, flip flop and shifting register<sup>[7–9]</sup>. Among most of those strategies, additional selecting devices seem requisite for realization of logical functions in memristor architecture. New materials, device architectures or new operation modes are demanded to be further proposed and developed.

Recently the integration of two dimensional materials (2DMs) into memristor has been a new

research focus in the electronic community, ranging from semimetallic graphene<sup>[10,11]</sup>, to the semiconducting transition metal dichalcogenides (TMDs)<sup>[12-14]</sup>, black phosphorus (BP)<sup>[15]</sup>, as well as two dimensional hexagonal boron nitride (h-BN)<sup>[16,17]</sup>, perovskite<sup>[18]</sup> and MXene<sup>[19]</sup>. Their dangling-bond-free interface, weak surface van der Waals interaction and atomically thin nature facilitate versatile and fantasy device properties in memristor architectures [20-22]: 1) 2DMs as electrode: for example, graphene with its high in plane carrier mobility and van der Waals interface (dimensional anisotropic, in other words) leads to both high mobility (10<sup>3</sup>cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) and high on-off ratio (10<sup>7</sup>) [23], and also a high thermal stability up to 340 °C[24,25]; 2) 2DMs as insertion layer: via well controlled defect density of graphene layer, the memristor could be switched between fast threshold switching (TS) mode with high on-state current and resistive switching (RS) memory mode of low power dissipation<sup>[5]</sup>; 3) 2DMs as switching layer: the atomic thin two dimensional insulator, such as perovskite and h-BN, could largely suppressed the leakage current in a metal/insulator/metal (MIM) structure, enable ultra-low operating current [18,26]; moreover, the surface native oxide of 2DMs uniform interfaces, such as SnO<sub>x</sub>/SnSe/SnO<sub>x</sub>, could also facilitate a random number generation for realization hardware-based Markov chain algorithm<sup>[27]</sup>; 4) 2DMs based photonic memristor: the supreme surface-to-volume ratio, strong photonic interactions and photo-generated charge trapping of 2DMs lead to non-volatile photonic memristor<sup>[28]</sup>. Among the 2DMs family, the new emerging layered bismuth oxyselenide (Bi<sub>2</sub>O<sub>2</sub>Se) have recently aroused lots of attentions in nano-electronic area due to its remarkable environmental stability, suitable band gap and high carrier mobility<sup>[29,30]</sup>. Determined with theoretical prediction and ARPES mapping, the Bi<sub>2</sub>O<sub>2</sub>Se exhibited very low in-plane electron effective mass ( $m^* = 0.14 \pm 0.02$  m<sub>0</sub> where  $m_0$  is the free-electron mass). This value is much lower than other semiconductor materials including traditional Si  $(0.26m_0)$  as well as two dimensional  $MoS_2$  (0.4-0.6  $m_0$ ) or black phosphorus (0.15  $m_0$  for  $m_x^*$  and 1.18  $m_0$  for  $m_y^*$ ), and thus suggested the promises to achieve ultra-high electron mobility. Experimentally, an ultrahigh mobility of 18500-28900 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at 1.9K has been exhibited in Hall measurements. Moreover, high field-effect mobility up to 1500 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> as well as large on/off ratio (10<sup>6</sup>), and nearly ideal subthreshold swing of 65 mV dec<sup>-1</sup> has been realized in transistor architecture. Those outstanding properties indicate Bi<sub>2</sub>O<sub>2</sub>Se could be a promising material for constructing high speed, low power electronic devices<sup>[31]</sup>. While, a Bi<sub>2</sub>O<sub>2</sub>Se based RS device is yet to be experimentally demonstrated  $^{[32,33]}$ . The role of the layered two-dimensional lattice structure  $Bi_2O_2Se$  in the RS type devices remain elusive.

In this work, a Bi<sub>2</sub>O<sub>2</sub>Se based MAGIC (Memristor Aided loGIC) has been proposed and characterized<sup>[34]</sup>. In the high contact voltage region, a slightly effective Schottky barrier was found at the Pd and Bi<sub>2</sub>O<sub>2</sub>Se interface. Due to this energy barrier, a small back electrode voltage is requisite for resistive switching to supply sufficient carrier densities injection. Moreover, via carefully modulating the electric field polarities, reconfigurable logic applications could be realized. To provide more knowledge on the Bi<sub>2</sub>O<sub>2</sub>Se-Pd interfaces and the mechanism of resistive switching, conductive atomic force microscopy and kinetic Monte Carlo simulation have been carried out. Specifically, the logical function realized in Bi<sub>2</sub>O<sub>2</sub>Se based memristor do not demand additional devices, which largely reduces the fabrication cost and circuit complexity. Thus the Bi<sub>2</sub>O<sub>2</sub>Se based MAGIC is a promising component toward practical in-memory logic computing and next generation nano-electronic applications.

#### 2. Results and Discussion:

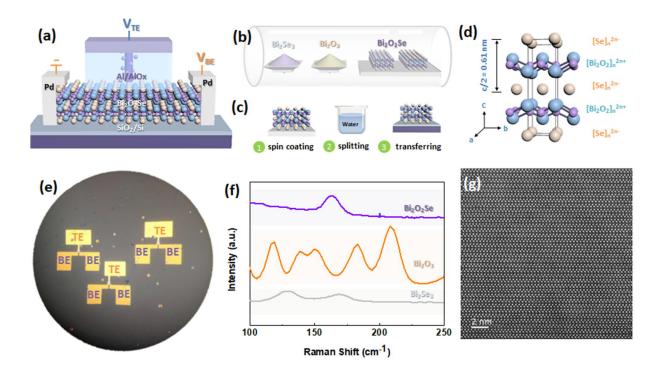

To prepare Bi<sub>2</sub>O<sub>2</sub>Se based memristor, low pressure chemical vapour deposition (LPCVD) process was carried out to synthesis Bi<sub>2</sub>O<sub>2</sub>Se (more synthesis details in Experiment), as shown in Figure 1(a), where Bi<sub>2</sub>O<sub>3</sub> and Bi<sub>2</sub>Se<sub>3</sub> powders were placed in the center and upstream of the chamber to generate vapour sources. Since the freshly cleaved mica exhibits a strong interaction with Bi<sub>2</sub>O<sub>2</sub>Se, it is a suitable substrate for lateral 2D growth<sup>[35]</sup>. After synthesis, transferring process was subsequently carried out, where the Bi<sub>2</sub>O<sub>2</sub>Se experienced including PMMA (poly (methyl methacrylate)) and PDMS (polydimethylsiloxane) coating, baking, water detaching, attaching to SiO<sub>2</sub>/Si substrate, and finally acetone and IPA (isopropanol) cleaning (Figure 1 (b)). To check the material phonon vibration, the Bi<sub>2</sub>O<sub>2</sub>Se have been probed via Raman spectra. As shown in Figure 1 (d), the characteristic A1g peak was observed at 159 cm<sup>-1</sup> via Raman spectrum probing, which is consistent with previous reports. The Bi<sub>2</sub>O<sub>2</sub>Se nanosheet is about 15 layers thick considering the theoretical thickness of 0.61 nm. The grain size is around 35 µm, which is sufficient for the subsequent device fabrication. The Bi<sub>2</sub>O<sub>2</sub>Se crystal in a tetragonal phase (I4/mmm, a = 3.891 Å, c = 12.21 Å and Z = 2) is shown in Figure 1(c). Within the crystal cell the Bi atom is covalently bonded with O atom to form a Bi<sub>4</sub>O tetrahedron, then the tetrahedrons share edges and arrange together to form [Bi<sub>2</sub>O<sub>2</sub>]<sub>n</sub><sup>2n+</sup> layers, which are alternately sandwiched with the negatively charged [Se]<sub>n</sub><sup>2n</sup>- layers. To further confirm its lattice structure, high resolution transmission electron microscope (HRTEM) was carried out. As shown in Figure 1 (f), the Bi<sub>2</sub>O<sub>2</sub>Se lattice in a cross sectional view, is in highly crystallized as theoretical prediction. After carefully transfer toward SiO<sub>2</sub> substrate, subsequently an Al/AlO<sub>x</sub>/Bi<sub>2</sub>O<sub>2</sub>Se memristor was fabricated, as demonstrated in Figure 1 (d) and the optical microscope image in Figure 1 (g) (more fabrication details in Experiment). 7 nm AlO<sub>x</sub> was prepared via pre-deposition of thin seeding Al layer combining with native oxide of top Al electrode. The AlO<sub>x</sub> served as a resistive switching medium, and the Al and Bi<sub>2</sub>O<sub>2</sub>Se serve as top and bottom electrode (TE and BE for short) respectively. Pd is chosen as the metal contact for Bi<sub>2</sub>O<sub>2</sub>Se due to its similar work function (5.1 eV) with Bi<sub>2</sub>O<sub>2</sub>Se (5.0 eV). Additional Pd contact leads to three-terminal memristor architecture, enabling more electrical measurements and device functions based on the Pd/Bi<sub>2</sub>O<sub>2</sub>Se interface.

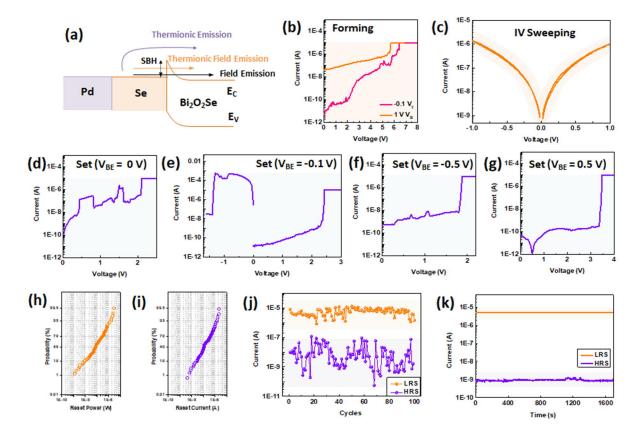

Figure 2 demonstrated the basic properties of Bi<sub>2</sub>O<sub>2</sub>Se based memristor. For generic RS memristor, the voltage was applied from TE side vertically and the BE side was normally grounded. While for the Bi<sub>2</sub>O<sub>2</sub>Se based memristor, the voltage given at the BE side is found requisite and highly related to the RS behaviours, as illustrated in the Figure. Started from the forming process, this initialization step is to create a conductive path to bridge the Al TE and Bi<sub>2</sub>O<sub>2</sub>Se BE, where compliance current was set as 10 μA to prevent permanent oxide hard breakdown. With two different voltages applied to the BE terminal (V<sub>BE</sub> for short), the different forming processes reflect on different IV curves, where the high V<sub>BE</sub> brings high injection current (from 10<sup>-7</sup> A) of the BE terminal and leads to smaller set voltage 1.76 V, while the low V<sub>B</sub> leads to much lower injection current (initial from 10<sup>-11</sup> A) and a much higher set voltage located at 3.36 V. Since the BE voltage is applied to the Pd contact, it is necessary to understand the electrical characteristics of the Pd-Bi<sub>2</sub>O<sub>2</sub>Se interface. Figure 2(b) shows the IV sweeping curves of the two Pd contacts. The voltage sweeping was ranged from -1 V to 1 V, and no hysteresis effect is found voltage region from – 100 mV to 100 mV, the current is linearity, which is consistent with previous reports. But for the higher voltage region (e.g. from ± 100 mV to ±500 mV), the IV curve becomes slightly nonlinearity. As illustrated in Figure 2 (a), the nonlinearity could be originated from thermionic emission, thermionic field emission and field emission (direct tunnelling)<sup>[36]</sup>. The effective Schottky barrier height (SBH) could be fitted with the following equation:

$$I = AA^*T^2e^{\frac{\phi_B}{k_BT}},\tag{1}$$

where A is the effective area,  $A^*$  is the Richardson constant, T is the temperature (300K), and  $k_B$  is the Boltzmann constant. Effective Schottky barrier height  $\emptyset_B$  could be derived as 0.078 eV and 0.066 eV for negative and positive branches respectively. After considering lattice structures, work function matching and the SBH, the transition from linearity to slightly nonlinear IV curve could be explained as following: in the small voltage region (within  $\pm$  100 mV), the current was concentrated at the surface Se layer and the ohmic contact was formed due to the work function matching between the interfacial Se layer of Bi<sub>2</sub>O<sub>2</sub>Se and the Pd contact. As for the higher voltage region ( $\pm$  100 mV to  $\pm$  1 V), the current flow is not only limited within the interfacial Se layer but also penetrated into Bi<sub>2</sub>O<sub>2</sub> layer. Then the current flow encountered the intrinsic energy barrier

between Se layer and Bi<sub>2</sub>O<sub>2</sub> layer, leading to the formation of nonlinear IV curve in both negative and positive branches. The derived effective SBH is much smaller than the band gap of Bi<sub>2</sub>O<sub>2</sub>Se is due to the edge contact structure between Bi<sub>2</sub>O<sub>2</sub>Se with the Pd contact, which compensates most of the current rectification effect induced by the SBH.

Based on the knowledge of the Bi<sub>2</sub>O<sub>2</sub>Se interface, the influence of the V<sub>B</sub> bias on the RS behaviour has been explored, including the -0.5 V, -0.1 V, 0 V and 0.5 V, as exhibits in Figure 2 (c, e-g). As for the case of 0 V V<sub>BE</sub>, significant unstable tunnelling current during the set process has been obtained, which has not been found in other conditions. It indicated that the  $V_{\text{BE}}$  bias is requisite for guaranteeing sufficient carrier densities for RS process. In this scenario, -0.1 V V<sub>BE</sub> is chosen for a normal case of the Bi<sub>2</sub>O<sub>2</sub>Se based memristor to analysis its RS phenomenon and explore the memory characteristics. A typical IV curve containing set and reset process is shown in Figure 2 (c), where the set voltage located at 2.38 V. Through analysis the electrical behaviour before set, more knowledge of the conduction within oxide layer and the interface of Bi<sub>2</sub>O<sub>2</sub>Se and AlO<sub>x</sub> layer could be derived. There are three typical conduction modes within the oxide layer, which is based on the relationship between injected carriers  $(n_1)$ , free carriers in thermal equilibrium ( $n_0$ , assuming T=300 K), and intrinsic defects or trap ( $n_T$ )<sup>[27,37]</sup>: the first region (approximately from 0 to 2 V) is in the Ohmic conduction ( $I \propto V$ ), where  $n_I + n_0 < n_T$ , followed with two short regions (approximately from 2 to 2.2 V and from 2.2 to 2.3V) in space-charge-limited-current conduction (SCLC,  $I \propto V^2$ ) and trap-filled limited (TFL,  $I \propto V^3$ ) conduction regions, where  $n_I+n_0>n_T$ , and  $n_I>n_0$ ,  $n_I>>n_0$  respectively. The low HRS current (in the  $10^{\text{-}11}\,\text{A}$  level) could be attributed to both the good quality of  $\text{AlO}_x$  layer to suppress the leakage current and also the two dimensional interface of Bi<sub>2</sub>O<sub>2</sub>Se and AlO<sub>x</sub> layer. Note that Bi<sub>2</sub>O<sub>2</sub>Se demonstrates obvious characteristics of 2D materials, but different from vdW layered materials such as graphene and  $MoS_2$ , the interaction between  $[Bi_2O_2]_n^{2n+}$ - $[Se]_n^{2n-}$  layers is electrostatic force instead of vdW force. Thus the unique strong injection region in other two dimensional material based memristor has not been found in the current study. Then reliability test were carried out including static reset current and power distribution (ranged from 100nA (nW) to 1µA (nW)), retention up to 1800s for both HRS/LRS (Figure 2 (d)), and endurance up to 100 DC resistive switching cycles (Figure 2 (e)). Those characteristics guarantee its robustness for the following logical operations. The key to realize the logical operation is to configurable control the set

voltage. As demonstrated in the Figure 2 (e,g), via providing two different  $V_{BE}$  bias ( $\pm 500$  mV), two distinct RS IV curve has been obtained. The dynamically tuning switching window is the key to realize logical operations in the current study, which will be analysis in the following study.

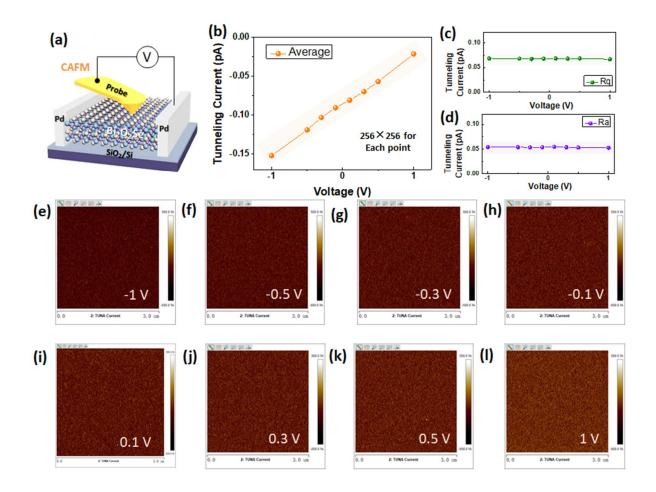

Based on electrical measurements, BE voltage was found to highly related with the Set behaviour. To support this scenario and obtain more knowledge on the Bi<sub>2</sub>O<sub>2</sub>Se and Pd interface, a conductive atomic force microscopy (C-AFM, NT-MDT Solver P47, SP-47) was carried out in this section, as illustrated in Figure 3 (a). To match with the CAFM probe stations, additional sample preparation were taken including cm-level electrode pre-pattering and Pd contact pad deposition, where the tip is physical contact with the Bi<sub>2</sub>O<sub>2</sub>Se sample and the metal pad connect with the sample holder. When a potential difference is applied between the tip and the sample, the currents across the sample can be recorded [38]. Different voltages, ranging from  $\pm 1$  V,  $\pm 0.5$  V,  $\pm 0.3$ V, ±0.1 V, were applied on the Pd side and the top electrode probe on the Bi<sub>2</sub>O<sub>2</sub>Se surface to collect tunnelling current, where the scanning area is  $3 \times 3 \mu m^2$  with 512 by 512 points (figure 3 (b, e-l)). Based on the current mapping, the current was found negatively and linearly related with the applied voltages. While for the local range from -0.5 V to -0.1 V and 0.1 V to 0.5 V, there is some non-linearity. This slightly non-linearity is in highly consistent with the electrical measurement, where small SBH exhibits in small voltage range in both negative and positive branches. The arithmetical mean deviation Ra and the root mean squared Rq are also obtained via current mapping. As exhibited in Figure 3 (c-d), the Ra and Rq values are in highly uniform, revealing that the two-dimensional Bi<sub>2</sub>O<sub>2</sub>Se surface is highly homogeneity and uniform. Moreover, the repetitive scanning at the atmosphere environment did not invoking detrimental effects onto the Bi<sub>2</sub>O<sub>2</sub>Se surface.

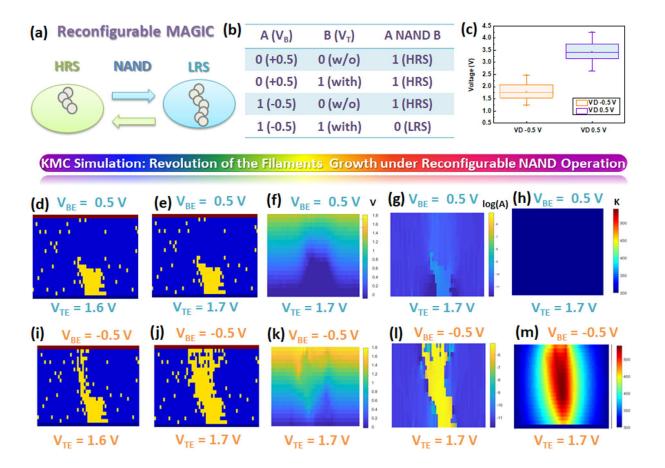

In this section, the  $Bi_2O_2Se$  based MAGIC has been experimentally demonstrated, containing a kinetic Monte Carlo simulation. The two resistant states of the  $Bi_2O_2Se$  based memristor, HRS and LRS, could be naturally seen as the out binary state (Y), "1" and "0" after logical operations, as shown in **Figure 4** (a). To realize logical operation, conditional inputs correlated with different output resistant states are requisite. Based on the above electrical measurements and materials analysis, the set window could be dynamically tuned by the  $V_{BE}$  bias. Thus the different  $V_{BE}$  and

$V_{SET}$  values could be seen as two conditional inputs, "A" and "B", where the  $\pm$  0.5 V  $V_{BE}$  and 2.5  $V/0\ V\ V_{TE}$  could be seen as binary "1" and "0" for "A" and "B". After carefully chosen the  $V_{BE}$ and V<sub>TE</sub> values, a NAND operation could be realized in the Bi<sub>2</sub>O<sub>2</sub>Se based memristor, where the truth table and operation algorithm are exhibited in Figure 4 (b). Considering the NAND gate is a universal gate, more logical functions could be realized via cascading NAND gates<sup>[8]</sup>. The current Bi<sub>2</sub>O<sub>2</sub>Se based MAGIC exhibits in-memory computing fashion, which owns at least three unique advantages as list below: i) zero static power dissipation because no power supply is needed to maintain its logical states<sup>[39]</sup>; ii) reconfigurable and stable, as demonstrated in Figure 4 (c); iii) no additional selecting devices are needed. As for the traditional silicon based one-diode-one-resistor structure, to fabricate the epitaxial silicon based selecting device, additional high temperature process is requisite. To provide more understanding on the logical operations, a kinetic Monte Carlo (KMC) simulation based on trap-assisted-tunnelling (TAT) model has been carried out [40,41]. The physical models including oxygen vacancy generation, injection, hopping, dynamic migration, recombination, and temperature updating, are described in the supporting information in detail<sup>[42]</sup>. As demonstrated in Figure 4 (d-m), the comparison of different V<sub>BE</sub> polarity are visualized including the revolution and distribution of oxygen vacancies, electric fields, current densities, and temperatures. Under same  $V_{TE}$  value (1.7 V), different  $V_{BE}$  ( $\pm$  0.5 V) lead to different resistive switching behaviours. These simulation results consistent with the electrical measurements, supported the logical operation algorithm, as well as provided more knowledge of the filament formation under different electric filed polarity at atomic level.

## 3. Conclusion

Briefly,  $Bi_2O_2Se$  based MAGIC has been proposed and experimentally demonstrated in the current study. The small SBH in the interface of  $Bi_2O_2Se$  and Pd contact and related the  $V_{BE}$  bias are found influential on the resistive switching behaviour. Via carefully chosen the  $V_{BE}$  and  $V_{TE}$  values, an in-memory logical computing algorithm has been realized. The surface probing via CAFM and a KMC simulation results consistent with the electrical measurements and also provide more knowledge on the  $Bi_2O_2Se$  surface as well as the resistive switching process. The current  $Bi_2O_2Se$  based MAGIC enables in-memory computing with reconfigurable and stable

logical operations, as well as zero static power dissipations, which facilitate constructing the field programmable circuit fabric, and is also highly desired in the areas including edge computing, wearable sensors, and the Internet of Things (IOT).

### 4. Experiment

CVD synthesis of Bi<sub>2</sub>O<sub>2</sub>Se on Mica: The 2D Bi<sub>2</sub>O<sub>2</sub>Se nanosheets were synthesized in a low-pressure CVD furnace equipped with a 3 inch diameter horizontal quartz tube and three temperature controlled zones. Powders of Bi<sub>2</sub>O<sub>3</sub> and Bi<sub>2</sub>Se<sub>3</sub> as precursors were placed in the central zone and upstream of the chamber with a distance of 8 cm, respectively. Ar gas was used as the carrier gas to transport the vaporized precursor to the targeting growth location of mica with a distance of 12 cm downstream. The tube was sealed, evacuated, and flushed with pure Ar gas to provide an oxygen-free environment. Typical growth conditions are described below. The temperature of Bi<sub>2</sub>Se<sub>3</sub> source was 500 °C. The system pressure was controlled at 100 Torr and the flow rate of the carrier gas was 200 sccm. Growth time ranged from 10 to 40 min. After the deposition was complete, the furnace was cooled naturally to room temperature and the quartz tube was refilled with Ar gas to reach atmospheric pressure.

Characterization of the Bi<sub>2</sub>O<sub>2</sub>Se nanosheets: After the material synthesis and transferring, A RAMaker confocal Raman spectrum with 100x objective lens with 473 nm excitation laser was carried out to probe its lattice information, where the spot size was approximately 0.5μm. A focused ion beam (FIB) in a dual beam microscope was employed to obtain the cross sectional images of the Bi<sub>2</sub>O<sub>2</sub>Se. The following lattice detecting was obtained via a high resolution transmission electron microscope (TEM, JEM-2100F, acceleration voltage 200 kV).

Fabrication of the Bi<sub>2</sub>O<sub>2</sub>Se based electronic device. Initially, a poly (methyl methacrylate) (PMMA) and polydimethylsiloxane (PDMS) assisted transfer was carried out to detach the Bi<sub>2</sub>O<sub>2</sub>Se nanosheet from mica substrate and assemble on the targeted SiO<sub>2</sub>/Si substrate. In each step, the sample was sequentially cleaned with acetone, isopropyl alcohol (IPA), and deionized (DI) water. After the transferring process, the Bi<sub>2</sub>O<sub>2</sub>Se sample was defined the metal contacts (50 nm Pd) and top dielectric and electrode (7 nm naturally formed AlO<sub>x</sub> and 50 nm Al), utilizing LED lithography. The deposition was via thermal evaporator and the deposition rate was confined within 1 Å at 10<sup>-6</sup> Torr to ensure the film uniformity and quality. Electrical properties were all measured in Agilent B1500 Semiconductor Device Parameter Analyzer.

### **Author contribution**

Bo Liu and Chao-Sung Lai generated the idea and designed the work. Dharmendra Verma prepared the sample. Bo Liu, Hanyuan Liang, Hui Zhu measured the device. Bo Liu, Lain-Jong Li, Tuo-Hung Hou, Chao-Sung Lai analysis the experiment results. Yudi Zhao carried out the Monte Carlo simulation. Bo Liu and Le An Wang prepared the manuscript, and Chao-Sung Lai revised it.

# Acknowledgements

We appreciate the discussion with Prof. Chia-Ming Yang and Dr. Tsung-Cheng Chen. This study was supported by grants from the Ministry of Science and Technology, Taiwan (MOST 109-2221-E-182-013-MY3, and 109-2622-8-182-001-TS1), and Chang Gung Memorial Hospital (CMRPD2K0051, and CMRPD2K0171).

# **Table of Content:**

Figure 1 Illustration of the device architecture of Bi<sub>2</sub>O<sub>2</sub>Se based memristor, fabrication process and material analysis. (a) the device structure of Bi<sub>2</sub>O<sub>2</sub>Se based memristor, (b) low pressure chemical vapour deposition of Bi<sub>2</sub>O<sub>2</sub>Se in a furnace, (c) transfer process of Bi<sub>2</sub>O<sub>2</sub>Se from mica substrate to SiO<sub>2</sub>/Si substrate, (d) the lattice structure of Bi<sub>2</sub>O<sub>2</sub>Se, (e) Optical Image of Bi<sub>2</sub>O<sub>2</sub>Se based memristor device, (f) Raman spectrum of Bi<sub>2</sub>O<sub>2</sub>Se as well its precursor Bi<sub>2</sub>O<sub>3</sub>, Bi<sub>2</sub>Se<sub>3</sub>, (g) HR-TEM image of the Bi<sub>2</sub>O<sub>2</sub>Se in cross section view, where the scale bar is 2 nm.

Figure 2 Basic electrical measurements of  $Bi_2O_2Se$  based Memristor. (a) Illustration of the band diagram of the interface between Pd contact and  $Bi_2O_2Se$ , as well as the current injection mechanisms, (b) forming process of the  $Bi_2O_2Se$  based memristor under different  $V_{BE}$  bias, (c) IV sweeping curve between the two contact Pd pads, (d, f-g) set process under  $V_{BE} = 0$ , -0.5 0.5V, (e) set and reset process under  $V_{BE} = -0.1$  V, (h-i) reset power and reset current distribution, and reliability test of (j) endurance and (k) retention, where the reading voltage is 0.1 V.

Figure 3 CAFM measurements of  $Bi_2O_2Se$  surface. (a) Illustration of the CAFM probe station, (b-d) Average, Rq and Ra values of the tunnelling currents, (e-l) the current mapping of CAFM in  $3 \times 3 \mu m^2$  with 512 by 512 points, under the sweeping bias ranging from -1 (e), -0.5 (f), -0.3 (g), -0.1 (h), 0.1 (i), 0.3 (j), 0.5 (k), 1 V (l).

Figure 4 the demonstration of Bi<sub>2</sub>O<sub>2</sub>Se based MAGIC and kinetic Monte Carlo simulation.

(a-b) the illustration figure and truth table of the MAGIC operations, (c) reconfigurable logical operations: each error bar contains 20 cycles; Monte Carlo simulation including filament revolution (d-e, i-j), distribution of electric field (f, k), current (g, l) and temperature (h, m) with different  $V_{\text{BE}}$  bias.

#### References:

- [1] D. Ielmini, H. S. P. Wong, *Nat. Electron.* **2018**, *1*, 333.

- [2] M. Lanza, H. S. P. Wong, E. Pop, D. Ielmini, D. Strukov, B. C. Regan, L. Larcher, M. A. Villena, J. J. Yang, L. Goux, A. Belmonte, Y. Yang, F. M. Puglisi, J. Kang, B. Magyari-Köpe, E. Yalon, A. Kenyon, M. Buckwell, A. Mehonic, A. Shluger, H. Li, T. H. Hou, B. Hudec, D. Akinwande, R. Ge, S. Ambrogio, J. B. Roldan, E. Miranda, J. Suñe, K. L. Pey, X. Wu, N. Raghavan, E. Wu, W. D. Lu, G. Navarro, W. Zhang, H. Wu, R. Li, A. Holleitner, U. Wurstbauer, M. C. Lemme, M. Liu, S. Long, Q. Liu, H. Lv, A. Padovani, P. Pavan, I. Valov, X. Jing, T. Han, K. Zhu, S. Chen, F. Hui, Y. Shi, Adv. Electron. Mater. 2019, 5, 1800143.

- Y. X. Zhou, Y. Li, N. Duan, Z. R. Wang, K. Lu, M. M. Jin, L. Cheng, S. Y. Hu, T. C. Chang,

H. J. Sun, K. H. Xue, X. S. Miao, Adv. Electron. Mater. 2018, 4, 1800229.

- [4] Z. R. Wang, Y. Li, Y. T. Su, Y. X. Zhou, L. Cheng, T. C. Chang, K. H. Xue, S. M. Sze, X. S. Miao, *IEEE Trans. Electron Devices* **2018**, *65*, 4659.

- [5] X. Zhao, J. Ma, X. Xiao, Q. Liu, L. Shao, D. Chen, S. Liu, J. Niu, X. Zhang, Y. Wang, R. Cao,

W. Wang, Z. Di, H. Lv, S. Long, M. Liu, Adv. Mater. 2018, 30, 1705193.

- [6] M. Oian, I. Fina, F. Sánchez, J. Fontcuberta, *Small* **2019**, *15*, 1805042.

- [7] Y. Zhou, Y. Li, L. Xu, S. Zhong, H. Sun, X. Miao, Appl. Phys. Lett. 2015, 106, 233502.

- [8] P. Huang, J. Kang, Y. Zhao, S. Chen, R. Han, Z. Zhou, Z. Chen, W. Ma, M. Li, L. Liu, X. Liu, Adv. Mater. 2016, 28, 9758.

- [9] L. Cheng, Y. Li, K. S. Yin, S. Y. Hu, Y. T. Su, M. M. Jin, Z. R. Wang, T. C. Chang, X. S. Miao, Adv. Funct. Mater. 2019, 29, 1905660.

- [10] B. Liu, Z. Liu, I. S. Chiu, M. Di, Y. Wu, J. C. Wang, T. H. Hou, C. S. Lai, ACS Appl. Mater. Interfaces 2018, 10, 20237.

- [11] F. Hui, E. Grustan-Gutierrez, S. Long, Q. Liu, A. K. Ott, A. C. Ferrari, M. Lanza, *Adv. Electron. Mater.* **2017**, *3*, 1600195.

- [12] M. Sivan, Y. Li, H. Veluri, Y. Zhao, B. Tang, X. Wang, E. Zamburg, J. F. Leong, J. X. Niu, U. Chand, A. V. Y. Thean, *Nat. Commun.* 2019, 10, 5201.

- [13] Y. Qiao, T. Hirtz, F. Wu, G. Deng, X. Li, Y. Zhi, H. Tian, Y. Yang, T.-L. Ren, *ACS Appl. Electron. Mater.* **2020**, *2*, 346.

- [14] X. F. Wang, H. Tian, Y. Liu, S. Shen, Z. Yan, N. Deng, Y. Yang, T. L. Ren, ACS Nano 2019,

- 13, 2205.

- [15] X. Yan, X. Wang, B. Xing, Y. Yu, J. Yao, X. Niu, M. Li, J. Sha, Y. Wang, AIP Adv. 2020, 10, 075013.

- [16] Y. Shi, X. Liang, B. Yuan, V. Chen, H. Li, F. Hui, Z. Yu, F. Yuan, E. Pop, H. S. P. Wong, M. Lanza, *Nat. Electron.* 2018, 1, 458.

- [17] S. Chen, M. R. Mahmoodi, Y. Shi, C. Mahata, B. Yuan, X. Liang, C. Wen, F. Hui, D. Akinwande, D. B. Strukov, M. Lanza, *Nat. Electron.* **2020**, *3*, 638.

- [18] H. Tian, L. Zhao, X. Wang, Y. W. Yeh, N. Yao, B. P. Rand, T. L. Ren, ACS Nano 2017, 11, 12247.

- [19] G. Ding, K. Zeng, K. Zhou, Z. Li, Y. Zhou, Y. Zhai, L. Zhou, X. Chen, S. T. Han, *Nanoscale* 2019, 11, 7102.

- [20] C. Y. Wang, C. Wang, F. Meng, P. Wang, S. J. Liang, F. Miao, *Adv. Electron. Mater.*2020, 6, 1901107.

- [21] G. Fiori, F. Bonaccorso, G. Iannaccone, T. Palacios, D. Neumaier, A. Seabaugh, S. K. Banerjee,L. Colombo, *Nat. Nanotechnol.* 2014, 9, 768.

- [22] L. Zhang, T. Gong, H. Wang, Z. Guo, H. Zhang, *Nanoscale* **2019**, *11*, 12413.

- B. Liu, H. H. Tai, H. Liang, E.-Y. Zheng, M. Sahoo, C. H. Hsu, T.-C. Chen, C. A. Huang, J.-C.

Wang, T.-H. Hou, C.-S. Lai, *Mater. Chem. Front.* 2020, 4, 1756.

- [24] M. Wang, S. Cai, C. Pan, C. Wang, X. Lian, Y. Zhuo, K. Xu, T. Cao, X. Pan, B. Wang, S. J. Liang, J. J. Yang, P. Wang, F. Miao, *Nat. Electron.* 2018, 1, 130.

- [25] B. Liu, I.-S. Chiu, C.-S. Lai, *Vacuum* **2017**, *137*, DOI 10.1016/j.vacuum.2016.11.022.

- [26] H. Zhao, Z. Dong, H. Tian, D. DiMarzi, M. G. Han, L. Zhang, X. Yan, F. Liu, L. Shen, S. J.Han, S. Cronin, W. Wu, J. Tice, J. Guo, H. Wang, *Adv. Mater.* 2017, 29, 1703232.

- [27] H. Tian, X. F. Wang, M. A. Mohammad, G. Y. Gou, F. Wu, Y. Yang, T. L. Ren, *Nat. Commun.*2018, 9, 4305.

- [28] X. Feng, X. Liu, K. W. Ang, *Nanophotonics* **2020**, *9*, 1579.

- [29] J. Wu, H. Yuan, M. Meng, C. Chen, Y. Sun, Z. Chen, W. Dang, C. Tan, Y. Liu, J. Yin, Y. Zhou, S. Huang, H. Q. Xu, Y. Cui, H. Y. Hwang, Z. Liu, Y. Chen, B. Yan, H. Peng, Nat. Nanotechnol. 2017, 12, 530.

- [30] T. Li, T. Tu, Y. Sun, H. Fu, J. Yu, L. Xing, Z. Wang, H. Wang, R. Jia, J. Wu, C. Tan, Y. Liang,

- Y. Zhang, C. Zhang, Y. Dai, C. Qiu, M. Li, R. Huang, L. Jiao, K. Lai, B. Yan, P. Gao, H. Peng, *Nat. Electron.* **2020**, *3*, 473.

- [31] C. Zhang, J. Wu, Y. Sun, C. Tan, T. Li, T. Tu, Y. Zhang, Y. Liang, X. Zhou, P. Gao, H. Peng, *J. Am. Chem. Soc.* **2020**, *142*, 2726.

- Z. Zhang, T. Li, Y. Wu, Y. Jia, C. Tan, X. Xu, G. Wang, J. Lv, W. Zhang, Y. He, J. Pei, C. Ma,

G. Li, H. Xu, L. Shi, H. Peng, H. Li, *Adv. Mater.* 2019, *31*, 1805769.

- [33] Y. Sun, J. Zhang, S. Ye, J. Song, J. Qu, Adv. Funct. Mater. 2020, 30, 2004480.

- [34] R. Ben Hur, N. Wald, N. Talati, S. Kvatinsky, *IEEE/ACM Int. Conf. Comput. Des. Dig. Tech.*Pap. ICCAD 2017, 2017-November, 225.

- [35] C. Yang, T. Chen, D. Verma, L. Li, B. Liu, W. Chang, C. Lai, Adv. Funct. Mater. 2020, adfm. 202001598.

- [36] D. S. Schulman, A. J. Arnold, S. Das, Chem. Soc. Rev. 2018, 47, 3037.

- [37] F. C. Chiu, H. W. Chou, J. Y. M. Lee, J. Appl. Phys. **2005**, 97, 103503.

- [38] B. Liu, M.-C. Hong, M. Sahoo, B. L. Ong, E. S. Tok, M. Di, Y.-P. Ho, H. Liang, J.-S. Bow, Z. Liu, J.-C. Wang, T.-H. Hou, C.-S. Lai, Adv. Mater. Technol. 2019, 4, DOI 10.1002/admt.201900422.

- [39] B. C. Jang, S. Y. Yang, H. Seong, S. K. Kim, J. Choi, S. G. Im, S. Y. Choi, *Nano Res.* 2017, 10, 2459.

- [40] X. Guan, S. Yu, H. S. P. Wong, *IEEE Trans. Electron Devices* **2012**, *59*, 1172.

- [41] S. Yu, X. Guan, H. S. P. Wong, *IEEE Trans. Electron Devices* **2012**, *59*, 1183.

- [42] P. Huang, S. Member, X. Y. Liu, B. Chen, S. Member, H. T. Li, *IEEE Trans. Electron Devices*2013, 60, 4090.