# Improvement on 1/f Noise Properties of Nitrided n-MOSFET's by Backsurface Argon Bombardment

P. T. Lai, Jing-Ping Xu, and Y. C. Cheng

Abstract—The 1/f noise properties of nitrided n-MOSFET's bombarded by low-energy (550 eV) argon-ion beam are investigated. It is found that after bombardment, 1/f noise, and its degradation under hot-carrier stress are reduced, and both exhibit a turnaround behavior with bombardment time for a given ion energy and intensity. The physical mechanism involved is probably enhanced interface hardness resulting from bombardment-induced stress relief in the vicinity of the oxide/Si interface. Moreover, from the frequency dependence of the noise, it is revealed that the nitrided devices have a nonuniform trap distribution increasing toward the oxide/Si interface which can be modified by the backsurface bombardment.

*Index Terms*— Backsurface bombardment, MOSFET's, nitridation, noise, oxide/Si interface.

### I. Introduction

XYNITRIDES have been considered as a promising gate dielectric for metal–oxide–semiconductor (MOS) devices due to their excellent robustness against hot-carrier stresses and radiation exposure, good blocking against diffusion of dopants and impurities, etc. [1]-[4]. However, the process of nitridation also leads to increases of oxide/Si interface-state density and 1/f noise [5], especially for NH<sub>3</sub>nitrided and N2O-grown oxynitrides, because the former suffers from hydrogen-related electron traps [6], [7], and the latter has an inferior structural transition layer with several defects near the oxide/Si interface, resulting from an initial accelerated growth phase [8]. Recently, the interface qualities of these oxynitrides have been improved by a backsurface Ar<sup>+</sup> bombardment technique [9], [10]. In this letter, it is further shown that 1/f noise properties of MOS devices with these two oxynitrides as gate dielectric are also largely improved after appropriate bombardment. This is very important because the capability of integrating low-noise analog circuits and high-speed digital circuits on the same chip is crucial to the production of a wide range of high-performance MOS integrated circuits.

# II. EXPERIMENTAL

The n-channel MOSFET's used in this study were fabricated on p-type (100) silicon wafers with a resistivity of 6–8  $\Omega$ -cm

Manuscript received October 1, 1998; revised November 23, 1998. This work was supported by RGC and CRCG grants.

P. T. Lai and Y. C. Cheng are with the Department of Electrical and Electronic Engineering, The University of Hong Kong, Hong Kong.

J. P. Xu is with the Department of Solid State Electronics, Huazhong University of Science and Technology, Wuhan 430074, China.

Publisher Item Identifier S 0741-3106(99)02490-8.

by self-aligned n<sup>+</sup> polysilicon gate process. The NH<sub>3</sub>-nitrded oxide (denoted as NO) was formed by thermally growing oxide at 1000 °C in Ar-diluted O2 followed by a nitridation at 1000 °C for 60 min in pure NH3, while N2O-grown oxide (denoted as N2OG) was prepared at 1050 °C for 120 min in pure N<sub>2</sub>O to give the same thickness of 250 Å as determined by capacitance-voltage measurements. Finally, the two kinds of samples were annealed at 950 °C for 25 min in N<sub>2</sub>. After completing all conventional processing steps, the samples were put into a vacuum chamber and a low-energy (550 eV) Ar<sup>+</sup> beam with an intensity of 0.5 mA/cm<sup>2</sup> was applied to directly bombard the backsurface of the wafers at room temperature under a vacuum of 3.2 mPa. Four different bombardment durations (0, 10, 20, and 40 min) were chosen, with the corresponding samples denoted as NO0, NO10, NO20, NO40, N2OG0, N2OG10, N2OG20, and N2OG40, respectively. Subsequently, the wafers were annealed in N<sub>2</sub> at 450 °C for 20 min. After all these processing steps, initial noise and interface properties of n-MOSFET's were characterized and then a hot-carrier stress with maximum substrate current ( $V_D = 2V_G = 8$  V) was performed to study their 1/f noise reliability. Using HP 35665A dynamic signal analyzer, BTA 9603 FET noise analyzer, and HP 4145B semiconductor parameter analyzer, 1/f noise was measured in the linear region of device operation  $(V_D = 0.2 \text{ V})$ for a gate overdrive voltage  $V_G^* = V_G - V_T = 0.5$  V at 50 Hz ( $V_T$  is the threshold voltage). The channel length Land width W of the n-MOSFET's were 2  $\mu$ m and 20  $\mu$ m, respectively. All measurements were carried out under lighttight and electrically shielded conditions.

### III. RESULTS AND DISCUSSIONS

The 1/f noise of MOSFET's is characterized by the noise power of drain current  $(S_{id})$  and can generally be approximated as [11]

$$S_{\rm id} = \alpha/f^{\gamma}$$

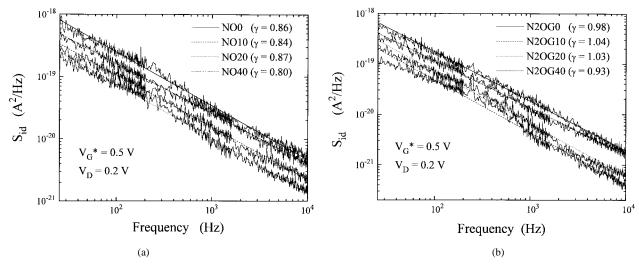

where  $\gamma$  is the noise exponent and  $\alpha$  is a constant for a given device structure and bias conditions. Fig. 1 is the measured drain-current noise power spectrum for all bombarded and nonbombarded samples. A common phenomenon can be observed from Fig. 1(a) and (b): bombardment firstly leads to noise decrease and then increase for a sufficiently long bombardment time, corresponding to a turnaround of 1/f noise magnitude as bombardment continues. The turnaround time is 20 min for the NO sample and 10 min for the N2OG

Fig. 1. Drain-current noise power spectrum of (a) NO samples and (b) N2OG samples with different bombardment times. The error of extracted  $\gamma$  value is  $\pm 0.003$ .

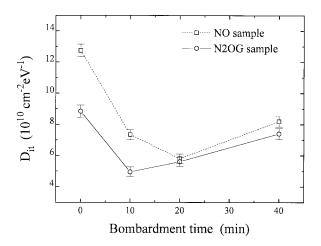

Fig. 2. Interface-state density before and after bombardment for different times (10, 20, and 40 min).

sample. From the number-fluctuation model [12], 1/f noise is attributed to fluctuation in the number of channel carriers arising from electronic tunneling transitions between interfacial traps and the inversion layer of MOSFET's. In other words,  $S_{\rm id}$  should be proportional to the density of the dielectric traps close to the oxide/Si interface  $(D_{it})$  which can be evaluated by the charge-pumping method. As shown in Fig. 2, a similar turnaround phenomenon is also observed in  $D_{it}$  of the same transistors used in noise measurement. The physical mechanism involved should be the stress compensation effect, where the ion bombardment at the wafer back induces a stress which can reduce the residual mechanical stress at the oxide/Si interface by up to 37% [13]. The resulting lower interfacial stress means lower  $D_{\mathrm{it}}$  and thus lower  $S_{\mathrm{id}}$ . Therefore, it can be believed that the residual stress at the interface is smaller in the N2OG sample than in the NO sample, and thus stress overcompensation causing the turnaround occurs earlier in the former than the latter. A possible explanation is that the higher the growth temperature (as for N2OG), the lower the residual stress in the oxide and at the oxide/Si interface [14]. In Fig. 1,

the straight lines represent a least-squares fit to the measured data and their slopes give the noise exponent shown in the parenthesis.  $\gamma \neq 1$  implies a nonuniform trap distribution along the direction normal to the oxide/Si interface [15], [16]. For a trap distribution that increases toward the interface, there are a large number of high-frequency traps (traps adjacent to the interface) giving rise to  $\gamma < 1$ . Otherwise,  $\gamma > 1$  due to a large number of low-frequency traps (traps farther away from the interface). Therefore, the extracted  $\gamma$  values support that both NH<sub>3</sub> nitridation and N<sub>2</sub>O growth produce a nonuniform trap distribution decreasing away from the interface due to hydrogen-related species for the former [6], [7], and an inferior structural transition layer with a lot of defects near the oxide/Si interface for the latter [8]. Also based on  $\gamma(NO) < \gamma(N2OG)$ , the former introduces more high-frequency traps than the latter due to the significant effects of the hydrogen species in NH<sub>3</sub>. As demonstrated by the N2OG sample, backsurface bombardment seems to preferentially affect high-frequency traps because they are closer to the interface:  $\gamma$  changes from <1 to >1 and then back to <1 as bombardment time increases. More specifically, 10- and 20-min bombardments greatly reduce high-frequency traps so that they become fewer than low-frequency traps and  $\gamma > 1$ . However, an excessive bombardment of 40 min generates many new high-frequency traps which, once again, outnumber low-frequency traps. For the NO sample, although the effect is not clearly seen, possibly due to a much higher interfacial oxide-trap density as shown in Fig. 2, a 40-min bombardment also gives rise to an obvious increase of high-frequency traps and thus a large reduction of  $\gamma$ .

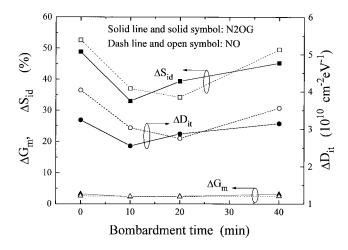

The effect of electrical stress on the 1/f noise of the devices is also examined. Fig. 3 shows a suppressed degradation of 1/f noise properties for all bombarded samples after a maximum-substrate-current stress ( $V_D=2$   $V_G=8$  V). As bombardment continues, the increase of 1/f noise ( $\Delta S_{\rm id}$ ) decreases to a minimum value for NO20 and N2OG10 samples, and then rebounds to a value comparable with those of nonbombarded samples, again exhibiting a turnaround behav-

Fig. 3. Increases of 1/f noise and interface-state density after a hot-carrier stress at  $V_D = 2$   $V_G = 8$  V for 3000 s for all samples.

ior similar to that in Fig. 1. In Fig. 3, interface-state creation  $(\Delta D_{\rm it})$  caused by the electrical stress is also plotted, and presents exactly the same trend as  $\Delta S_{id}$ , indicating that enhanced interface hardness induced by appropriate backsurface bombardment is responsible for the suppressed  $\Delta D_{\rm it}$  and hence the improvement of 1/f noise properties. Therefore, an optimal bombardment time should be chosen for a given ion energy and intensity to obtain the best interface and thus 1/f noise properties. As for degradation of peak linear transconductance  $(\Delta G_m)$  shown in Fig. 3, although it also exhibits a turnaround similar to those of  $\Delta S_{id}$  and  $\Delta D_{it}$ , much smaller value is observed, indicating that static parameters of MOSFET's are not as sensitive as dynamic parameters, e.g., 1/f noise, in assessing the device damage due to electrical stresses.

### IV. SUMMARY

Backsurface  $Ar^+$  bombardment can result in better 1/fnoise properties of nitrided n-MOSFET's which exhibit a turnaround behavior with bombardment time. Moreover, increase of 1/f noise under hot-carrier stress is also greatly suppressed for properly-bombarded samples. The involved mechanism is attributed to improved oxide/Si interface quality resulting from stress relief near the interface induced by the bombardment. In addition, 1/f noise measurements show that NH<sub>3</sub> nitridation introduces much more interfacial traps than N<sub>2</sub>O growth due to hydrogen-related species, and both give a nonuniform trap distribution near the oxide/Si interface which increases toward the interface. However, bombardment can greatly reduce interfacial oxide traps and thus change their distribution even to one decreasing toward the interface. Therefore, proper backsurface bombardment is effective to further increase interface hardness and decrease 1/f noise of nitrided MOSFET's. Moreover, since similar results have been obtained for much larger gate-oxide thickness of 5000 Å [13], under suitable bombardment conditions, this technique should be applicable to thicknesses below 100 Å.

### ACKNOWLEDGMENT

The authors would like to thank M. Q. Huang, G. Q. Li, and S. H. Zeng for their support in Ar<sup>+</sup> bombardment.

## REFERENCES

- [1] T. Hori, H. Iwasaki, and K. Tsuji, "Electrical and physical properties of ultrathin reoxidized nitrided oxides prepared by rapid thermal processing," IEEE Trans. Electron Devices, vol. 36, p. 340, 1989.

- H. Fududa, M. Yasuda, T. Iwabuchi, and S. Ohno, "Novel N2Ooxynitridation technology for forming highly reliable EEPROM tunnel oxide films," IEEE Electron Device Lett., vol. 12, p. 587, 1991.

- Y. L. Wu and J. G. Hwu, "Improvement in radiation hardness of reoxidized nitrided oxide (RNO) in the absence of post-oxidation anneal," IEEE Electron Device Lett., vol. 14, Jan. 1993,

- J. S. Cable, R. A. Mann, and J. C. S. Woo, "Impurity barrier properties of reoxidized nitrided oxide films for use with p<sup>+</sup> doped polysilicon

- gates," *IEEE Electron Device Lett.*, vol. 12, p. 128, 1991. [5] R. Jayaraman and C. Sodini, "1/f noise interpretation of the effect of gate oxide nitridation and reoxidation on dielectric trap," IEEE Trans. Electron Devices, vol. 37, p. 305, 1990.

- [6] P. Pan, "Characteristics of thermal SiO<sub>2</sub> films during nitridation," J. Appl. Phys., vol. 61, p. 284, 1986.

- Z. H. Liu, H.-J. Wann, P. K. Ko, C. Hu, and Y. C. Cheng, "Effects of N2O anneal and reoxidation on thermal oxide characteristics," IEEE Electron Device Lett., vol. 13, p. 402, 1992.

- [8] H. R. Soleimani, A. Philipossian, and B. Doyle, "A study of the growth

- kinetics of SiO<sub>2</sub> in N<sub>2</sub>O," in *IEDM Tech. Dig.*, 1992, p. 629. P. T. Lai, J. P. Xu, H. B. Lo, and Y. C. Cheng, "A study on interface and charge trapping properties of nitrided n-channel metaloxide-semiconductor field-effect transistors by backsurface argon bom-

- bardment," *J. Appl. Phys.*, vol. 82, no. 4, p. 1947, 1997. [10] J. P. Xu, P. T. Lai, and Y. C. Cheng, "A comparison between the interface properties of N2O-nitrided and N2O-grown oxides," Solid-State Electron., to be published.

- [11] K. K. Hung, P. K. Ko, C. Hu, and Y. C. Cheng, "A unified model for the flicker noise in metal-oxide-semiconductor field-effect transistors," IEEE Trans. Electron Devices, vol. 37, p. 654, 1990.

- [12] A. L. McWhorter, "1/f noise and germanium surface properties," in Semiconductor Surface Physics. Philadelphia, PA: Univ. Pennsylvania Press, 1957, p. 207.

- [13] M. Q. Huang, P. T. Lai, J. P. Xu, S. H. Zeng, G. Q. Li, and Y. C. Cheng, "Suppression of hot-electron-induced intewrface degradation in metal-oxide-semiconductor devices by backsurface argon bombardment," Microelectron. Reliab., to be published, 1998.

- P. Sutardja, W. G. Oldham, and D. B. Kao, "Modeling of stress-effects in silicon oxidation including the nonlinear viscosity of oxide," in IEDM Tech. Dig., 1987, p. 264.

- [15] S. Christensson, I. Lundstrom, and C. Svensson, "Low frequency noise in MOS transistors—I theory," Solid State Electron., vol. 11, p. 797,

- C. Surya and T. Y. Hsiang, "Theory and experiment on the 1/f noise in p-channel metal-oxide-semiconductor field-effect transistors at low drain bias," Phys. Rev. B, vol. 33, no. 7, p. 4898, 1986.