# Effects of NO Annealing and $GaO_xN_y$ Interlayer on GaN Metal-Insulator-Semiconductor Capacitor with $SiO_2$ Gate Dielectric

L. M. Lin and P. T. Lai<sup>2</sup>

Department of Electrical and Electronic Engineering, The University of Hong Kong, Hong Kong

$SiO_2$  was deposited on GaN by radio-frequency sputtering to fabricate metal-insulator-semiconductor (MIS) capacitors. Before the deposition, an ultrathin  $GaO_xN_y$  interlayer was thermally grown on the GaN wafer to improve the quality of the insulator/GaN interface. The interface-trap density at 0.4 eV below the conduction bandedge was reduced by one order compared with that of a sample without the  $GaO_xN_y$  interlayer. Annealing in NO gas at  $800^{\circ}$ C was conducted on both samples, and turned out to greatly suppress their oxide charges. The NO-annealed sample with the  $GaO_xN_y$  interlayer achieved the lowest oxide-charge density of  $1.7 \times 10^{11}$  cm<sup>-2</sup>, as compared to  $9.5 \times 10^{11}$  cm<sup>-2</sup> for its counterpart without the  $GaO_xN_y$  interlayer and about  $8.0 \times 10^{12}$  cm<sup>-2</sup> for the two nonannealed samples. Moreover, the NO annealing was found to effectively reduce border traps. Secondary-ion mass spectrometry analysis was performed to explain how the  $GaO_xN_y$  interlayer and NO annealing affect the performance of the GaN MIS capacitors.

© 2007 The Electrochemical Society. [DOI: 10.1149/1.2429043] All rights reserved.

Manuscript submitted June 20, 2006; revised manuscript received October 10, 2006. Available electronically January 16, 2007.

As wide-bandgap III-V material, GaN has brought great interest to optical applications: high-efficiency light-emitting diodes, ultraviolet photodetectors, and laser diodes. Based on the advantages of high critical electric field (up to 3 MV/cm) and low thermal generation rate, GaN is also suitable for fabricating high-power and hightemperature devices, such as metal-semiconductor field-effect transistor, metal-insulator-semiconductor field-effect transistor (MISFET), and high-electron-mobility transistor. 4.5 Although AlGaN/GaN heterostructure field-effect transistor has advantages over MISFET such as high two-dimensional electron-gas density and high carrier mobility, it suffers from large gate leakage and current collapse. As a result, GaN MISFET also received much attention due to its normally off nature and relatively lower gate-applied as its gate dielectric. However, leakage current through the gate dielectric, interface quality, and charges in the dielectric are major obstacles. Native Ga<sub>2</sub>O<sub>3</sub> achieved low interface-state density  $D_{\rm it}$ , but its leakage current was high.  $^2$  In order to improve the interface quality and breakdown field, SiO2 stacked with thermally grown Ga<sub>2</sub>O<sub>3</sub> was prepared by growing 15 nm Ga<sub>2</sub>O<sub>3</sub> and 35 nm Ga oxynitride, and then sputtering 100 nm SiO<sub>2</sub>. <sup>12</sup> In this paper, we show that a much thinner (~4 nm) thermally grown GaO<sub>x</sub>N<sub>y</sub> can effectively reduce interface traps, and the negative effects of GaO<sub>x</sub>N<sub>y</sub> on breakdown field and gate leakage current can be minimized by increasing the thickness ratio of SiO2 to GaOxNy, Lowpressure chemical-vapor deposited SiO2 annealed in NO or NH3 at 1100°C for 5 min was found to increase the leakage current and degrade the performance of GaN capacitor. 13 In this work, both stacked (SiO2/GaOxNy/GaN) and nonstacked (SiO2/GaN) structures were annealed in NO at a lower temperature of 800°C for 1 h, and as a result, showed less oxide charges and border traps. In addition, the effects of the NO annealing on interface states and breakdown field are discussed. Last, a microscopic analysis was done by secondary-ion mass spectrometry (SIMS) to explain how the GaO<sub>x</sub>N<sub>y</sub> interlayer can improve the interface quality, and how the NO annealing can reduce the oxide charges.

Fabrication of devices.— GaN wafers used in this study were prepared by metallorganic chemical-vapor deposition on c-plane sapphire. A 25 nm undoped GaN buffer layer was grown at  $550^{\circ}$ C and then 1  $\mu$ m epitaxial n-type GaN was grown at  $1170^{\circ}$ C. The epitaxial GaN layer was intentionally doped with Si to  $5 \times 10^{17}$  cm<sup>-3</sup>. Four wafers were cleaned by the standard RCA

method and then dipped into 1:1 HF solution to remove the native oxide and contaminants. <sup>14</sup> Two wafers were loaded into a furnace at 300°C, and the temperature was raised to 800°C in nitrogen ambient. Then, an oxidation was performed at 800°C in diluted oxygen  $(O_2: N_2 = 1:4)$  for 15 min. Because 200 nm  $GaO_xN_y$  could be formed in pure oxygen for 12 h at 800°C in our system, the GaO<sub>x</sub>N<sub>y</sub> interlayer was estimated to be less than 4 nm. Then, a layer of SiO<sub>2</sub> was deposited on all the samples, producing two with SiO2/GaOxNy stacked gate dielectric. The thickness of SiO2 was measured to be 40 nm with an error of 0.5 to 3% by a variable-angle spectroscopic ellipsometer from J. A. Wollam Co., Inc. After that, one stacked sample was annealed at 800°C in nitrogen, denoted as S-N2; another was annealed in NO, denoted as S-NO. The two nonstacked samples without the GaO<sub>3</sub>N<sub>y</sub> interlayer were annealed also at 800°C in N2 and NO, and denoted as NS-N2 and NS-NO, respectively. Finally, Al was thermally evaporated as electrodes for all the samples and then annealed in argon at 410°C for 30 min for good ohmic contacts. The area of the resulting capacitors was 7.85  $\times$  10<sup>5</sup> cm<sup>2</sup>. High-frequency (1 MHz) capacitance-voltage characteristics were measured by using an HP4284A LCR meter with a bias sweep rate of 0.1 V/s. The current-voltage (I-V) characteristics were measured by an HP4156B semiconductor parameter analyzer. All measurements were conducted in a dark ambient at room temperature.

# Results and Discussion

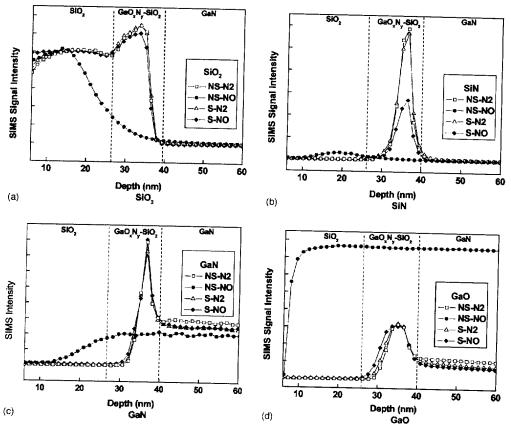

SIMS .-- The SIMS results of the four samples are shown in Fig. la-d. The top 5 nm signals are omitted due to the instability of SIMS signals at the sample surface. The curves have been adjusted along the x-axis due to the difference in dielectric thickness, thus providing clearer comparison. There are similar peak intensities of SiO<sub>2</sub>, SiN, GaN, and GaO for the NS-N2, S-N2, and S-NO samples in the transition region, while the intensity variations vs depth for the NS-NO sample are gradual with no elements piling up at the interface. It has been reported that the diffusivity (D) of Ga in SiO<sub>2</sub> is about 2 to 6 orders of magnitude higher than those of B, P, Al, Sb in SiO<sub>2</sub>. <sup>15</sup> This high diffusivity makes it possible to implant Ga through a 5000 Å SiO<sub>2</sub> layer into the underlying Si, and then a 30 min annealing at 800°C in  $N_2$  resulted in significant diffusion of the implanted Ga ( $D = 2.9 \times 10^{-15}$  cm<sup>2</sup>/s). At 800°C, Si can diffuse into GaN to a distance of about 30 Å ( $D = 1.9 \times 10^{-17}$  cm<sup>2</sup>/s, calculated based on the values in Ref. 17).<sup>17</sup> In brief, Ga can diffuse in SiO2 about 100 times faster than Si in GaN. Therefore, we can conclude that Ga out-diffusion into SiO2 is the main reason for the formation of SiGaON glass at the interface or in the dielectric layer.

The NS-NO sample has characteristics quite different from the

' E-mail: laip@eee.hku.hk

Figure 1. SIMS profiles of the GaN MIS capacitors. (a)  $\mathrm{SiO}_2$ , (b)  $\mathrm{SiN}$ , (c)  $\mathrm{GaN}$ , (d)  $\mathrm{GaO}_2$

other three: (i) the intensities of SiO2 and SiN gradually decrease from the surface of the dielectric to the interface, (ii) the intensity of GaN gradually increases from the surface to the interface, (iii) the GaO intensity remains high from the surface to the GaN substrate. The above three characteristics clearly demonstrate that a large amount of Ga has outdiffused into the SiO2 dielectric. The reason why the NS-NO sample has much more Ga diffusing into  $SiO_2$ compared with the same structure annealed in N2 (NS-N2) should be because the N and O decomposed from NO can have chemical reaction with Ga ions, and thus Ga ions have higher chance to diffuse into the dielectric under the oxidizing ambient. The diffused Ga could damage the lattice structure of SiO2 and produce defects, which trigger large leakage current. However, according to the S-NO sample, many fewer Ga ions diffuse into the SiO2 dielectric. This should be associated with the presence of the GaO<sub>x</sub>N<sub>y</sub> interlayer because Ga-O and O-N bonds are much more stable than Ga-N bonds under the oxidizing ambient. Moreover, the peak intensity of SiN in the transition layer is even lower than those of the two samples annealed in nitrogen. This is probably related to the fact that the N released from NO can react with the Si near the SiO<sub>2</sub>/GaN interface to form Si oxynitride, which can block the nitrogen out-diffusion from the GaN substrate more effectively than SiO<sub>2</sub>.

Positive oxide charges.— Although the SIMS profiles of the NS-NO and S-NO samples are quite different, a common feature is a significant reduction of positive oxide charges induced by the NO annealing. Figure 2a and b shows the high-frequency capacitance-

voltage (HF *C-V*) characteristics of the four samples, and Table I presents the device parameters extracted from the HF *C-V* curves (average values from six sample points).

The oxide thickness is calculated from the oxide capacitance  $C_{\rm ox}$ , which is approximated by the maximum value in the accumulation region. After annealing, the films become denser and their thicknesses calculated from  $C_{\rm ox}$  are a little bit smaller than the original 40 nm. For the samples NS-N2, S-N2, and NS-NO, the interdiffusion mainly happens near the interface (Fig. 1), and thus would not have significant effect on their dielectric constants. As for the sample S-NO, although there is more interdiffusion (Fig. 1), its dielectric constant hardly changes due to little changes in its oxide thickness and  $C_{\rm ox}$ . The chemical compositions of the four oxide films have little changes after annealing, and therefore, the dielectric constant used for calculation is taken to be that of SiO<sub>2</sub> (3.9).

The capacitance at the flatband voltage is as follows

$$C_{\rm fb} = \frac{C_s C_{\rm ox}}{C_s + C_{\rm ox}}$$

[1]

where

$$C_{s} = \varepsilon_{\text{GaN}} \varepsilon_{0} / L_{D}$$

[2]

$$L_D = (kT \varepsilon_{\text{GaN}} \varepsilon_0 / q^2 N_d)^{1/2}$$

[3]

$\varepsilon_{\rm GaN}$  is the dielectric constant of GaN;  $\varepsilon_0$  is the permittivity of free space;  $L_D$  is the Debye length;  $N_d$  is the actual carrier concentration (1.1  $\times$  10<sup>17</sup> cm<sup>-3</sup>) calculated from the measured capacitance; k is the Boltzmann's constant, and T is the measurement temperature

Figure 2. Measured and ideal C-V curves of the GaN MIS capacitors with  $SiO_2$  or stacked dielectric. (a) Annealed in  $N_2$ , (b) annealed in NO.

(298 K). Oxide-charge density  $Q_{\rm ox}$  is determined from the shift of flatband voltage

$$V_{\rm lb} = \Phi_{\rm Al,GaN} - \frac{Q_{\rm ox}}{C_{\rm ox}}$$

[4]

$$\Phi_{AI,GaN} = \chi + E_g/2 - (kT/q)\ln(N_d/n_i)$$

[5]

where  $\phi_{Al,GaN}$  is the work-function difference between Al and GaN;  $\chi$  is the electron affinity of GaN (4.07 eV);  $n_i$  is the intrinsic carrier concentration of GaN at room temperature (2.0 × 10<sup>-10</sup> cm<sup>-3</sup>);  $^{18}E_g$  is the forbidden bandgap of GaN (3.4 eV). After the NO annealing, the HF C-V curve shifts right, resulting in the lowest oxide-charge density of 1.8 × 10<sup>11</sup> cm<sup>-2</sup> for the S-NO sample, followed by the NS-NO sample at 9.5 × 10<sup>11</sup> cm<sup>-2</sup>, with  $Q_{ox}$  of the former more than one order lower than those of the two N<sub>2</sub>-annealed samples.

During the SiO<sub>2</sub> sputtering process, high-energy  $Ar^+$  ions bombard the SiO<sub>2</sub> target and knock off its molecules. First, the SiO<sub>2</sub> molecules have many dangling bonds. Second, these high-energy molecules to be deposited on the GaN wafer can break the GaN bonds, thus creating more dangling bonds. These dangling bonds of the Si or Ga ions should be the reason for the large  $Q_{\rm Ox}$  of the two N<sub>2</sub>-annealed samples (NS-N2 and S-N2). However, through the NO annealing for the NS-NO and S-NO samples, sputtered SiO<sub>2</sub> can also achieve low oxide-charge density, which should be due to the N and O decomposed from NO forming bonds with the Si or Ga ions.

Border traps.— Oxide traps close to the interface which can communicate with the semiconductor are called border traps,  $^{19}$  whose density  $(Q_{\rm hl})$  can be calculated by the following formula

$$Q_{\rm bt} = C_{\rm ox} \Delta V_{\rm FB} / (q \times d)$$

[6]

$\Delta V_{\rm FB}$  is the hysteresis at flatband between opposite sweeping directions of gate voltage; d is the distance in the oxide above the GaN surface ( $\sim 30$  Å). The hysteresis is due to the difference in gate biases at which electrons fill the traps and escape from the traps, or the difference between the capture and emission times of the border traps. In Table I, it can be seen that after the NO annealing, the border traps are reduced for both the NS-NO and S-NO samples. The NS-NO sample achieved the lowest border-trap density of  $1.2 \times 10^{17}$  cm<sup>-3</sup>, which should be related to the decrease of oxide charges after the NO annealing, as mentioned in the previous section.

Interface traps.— Interface-trap density is calculated based on the HF C-V curve by using the Terman method. <sup>20</sup> The interface traps follow the change in gate bias and cause a stretch-out of the HF C-V curve. The ideal capacitance is calculated by the following equation <sup>21</sup>

$$C_{\text{ideal}} = \frac{C_s C_{\text{ox}}}{C_s + C_{\text{ox}}}$$

[7]

where surface capacitance  $C_c$  is

$$C_s = \frac{C_{\text{FBS}}}{\sqrt{2}} \frac{\exp(\nu_s) - (n_i/N_d)^2 \exp(-\nu_s) - 1}{[-(\nu_s + 1) + \exp(\nu_s) + (n_i/N_d)^2 \exp(-\nu_s)]^{1/2}}$$

[8]

with carrier concentration  $N_d$  given by

$$N_d = \frac{2}{q\varepsilon_{\text{GaN}}\varepsilon_0 A^2 d(1/C^2)/dV}$$

[9]

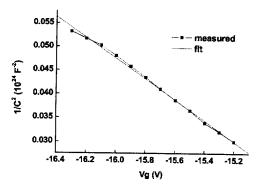

As Fig. 3 shows,  $N_d$  is fitted for the gate voltage ranging from -15.2 to -16.3 V based on the measured HF C-V curve of the S-N2 sample. Any fitting error is probably due to the nonuniformity of doping concentration or the interface traps. In order to compare the interface quality of different samples, the same  $N_d(1.1 \times 10^{17} \, \text{cm}^{-3})$  is used in all calculations. Figure 2a and b shows the difference between the ideal and measured C-V curves. The ideal curves are shifted along the x-axis because the interface-state density is not related to the shift of flatband voltage but only the shape

Table I. Electrical and physical parameters of the GaN MIS capacitors extracted from the high-frequency C-V curves.

| Sample                                                                                           | NS-N2                          | NS-NO                                         | S-N2                                          | CAYO                           |

|--------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------|-----------------------------------------------|--------------------------------|

| $T_{ m ox}$ (Å)<br>$V_{ m EB}$ (V)<br>$Q_{ m ox}$<br>( $	imes 10^{11}~{ m cm}^{-2}$ )            | 379<br>-13.4<br>77.2           | 381<br>-1.6<br>9.5                            | 380<br>-14.4<br>85.0                          | S-NO<br>390<br>-0.21<br>1.8    |

| $D_{ii}$ @<br>$E_c - E_t = 0.4 \text{ eV}$<br>$(\times 10^{10} \text{ cm}^{-2} \text{ eV}^{-1})$ | 120                            | 63                                            | 5.9                                           | 160                            |

| $Q_{\rm bi} \times 10^{17}  (\rm cm^{-3})$<br>$J_{\rm leakage} \oplus E_{\rm BD}$                | 2.6<br>65 mA/cm²@<br>4.9 MV/cm | 1.2<br>1.2 mA/cm <sup>2</sup> @<br>0.23 MV/cm | 2.7<br>1.2 mA/cm <sup>2</sup> @<br>0.93 MV/cm | 2.0<br>I mA/cm²@<br>1.79 MV/cm |

**Figure 3.** Typical capacitance characteristic of the GaN MIS capacitors vs gate voltage. Carrier concentration obtained by the fitting is  $1.1 \times 10^{17} \, \mathrm{cm}^{-3}$ .

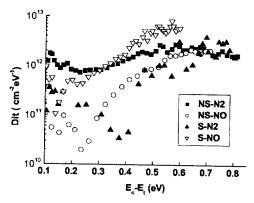

of the curve. The S-N2 sample has the smallest stretch-out from the ideal curve, indicating least interface traps among all the samples. The interface-trap distribution from 0.1 to 0.8 eV below the conduction band is shown in Fig. 4. Obviously, although the deep-level traps close to the midgap are hardly affected by thermally growing a Ga oxynitride interlayer or annealing in NO, the shallow traps close to the conduction band can be greatly suppressed. However, for the stacked sample annealed in NO, the shallow traps increase, probably due to excessive accumulation of nitrogen at the interface. Specifically, Table I shows that at 0.4 eV below the conduction bandedge, the S-N2 sample achieves a low interface-trap density of 5.9  $\times$  10  $^{10}$  cm  $^{-2}$  , followed by the NS-NO sample with 6.3  $\times$  10  $^{11}$  cm  $^{-2}$  , 1.2  $\times$  10  $^{12}$  cm  $^{-2}$  for the NS-N2 sample, and 1.6 imes  $10^{12}~{

m cm^{-2}}$  for the S-NO sample. The relatively high interface-trap density of the NS-N2 sample should be related to sputtering-induced damage of crystalline structure and large amount of dangling bonds formed at the interface. The S-N2 sample has fewer interface traps, possibly due to the formation of a GaO<sub>x</sub>N<sub>v</sub> interlayer through oxidation before the sputtering deposition. This interlayer can work as a buffer layer to reduce the damage of the GaN surface caused by the ensuing sputtering. Moreover, because GaO has higher binding energy than  $GaN_{v}^{22}$  the  $GaO_{x}N_{v}$  interlayer is more resistant to highenergy bombardment, thus forming a more passivated interface. The NO annealing has different effects on the stacked and nonstacked samples. For the nonstacked sample (NS-NO), it presents improved interface quality, which should be due to the N or O decomposed

Figure 4. Interface-trap density of the GaN MIS capacitors vs energy (from 0.1 to 0.8 eV below the conduction band) extracted from the high-frequency C-V curves.

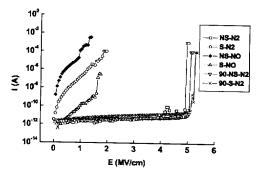

Figure 5. Typical leakage current of the GaN MIS capacitors vs electric field E. (Samples 90-SiN2 and 90-GaN2 have a thicker SiO<sub>2</sub> of 90 nm.)

from NO forming bonds with the dangling bonds of the Ga or Si ions at the interface, and thus results in a much smoother interface. However, after the stacked sample is annealed in NO (S-NO), the interface traps increase significantly, implying that too many nitrogen and oxygen atoms (decomposed from NO) piling up at the interface could also introduce traps and deteriorate the performance of devices. It is believed that by reducing the NO concentration in annealing, shortening annealing time, or lowering annealing temperature, the SiO<sub>2</sub>/Ga<sub>2</sub>O<sub>3</sub>/GaN system annealed in NO could achieve fewer oxide charges as well as fewer interface traps.

Breakdown field (EBD) and leakage current.—Figure 5 shows the current vs electric-field (1-E) characteristic. The electric field is estimated by using the total equivalent thickness calculated from  $C_{\rm ox}$ , with an error of about 5% due to the interlayer in the samples. The NS-N2 sample has the best I-E characteristic and lowest leakage current through the gate dielectric. The  $E_{\mathrm{BD}}$  of the NS-N2 sample is as high as 4.9 MV/cm ( $J_{\text{leakage}} = 65 \, \mu\text{A/cm}^2$ ), followed by 1.79 MV/cm ( $J_{\text{leakage}} = 1 \, \text{mA/cm}^2$ ) for the S-NO sample, 0.93 MV/cm ( $J_{\text{leakage}} = 1.2 \, \text{mA/cm}^2$ ) for the S-N2 sample, and 0.23 MV/cm ( $J_{\text{leakage}} = 1.2 \text{ mA/cm}^2$ ) for the NS-NO sample. After annealing in NO, the leakage current of the NS-NO sample increased significantly due to a large amount of Ga outdiffused into the dielectric. However, for the sample with GaO<sub>x</sub>N<sub>y</sub> interlayer, improved I-E characteristic was achieved by annealing in NO (the S-NO sample vs the S-N2 sample), which should be related to reduced oxide charges and defects in the dielectric. Compared with the nonstacked sample NS-N2, the stacked sample S-N2 presents degraded I-E characteristic, which should be due to the negative effects of the thermally grown GaO<sub>x</sub>N<sub>y</sub> interlayer. Stacked and nonstacked samples with thicker SiO2 were also fabricated by sputtering. In Fig. 4, the 90-NS-N2 sample means 90 nm  $\mathrm{SiO}_2$  was deposited on GaN, while the 90-S-N2 sample had 90 nm SiO2 deposited on the same GaO<sub>x</sub>N<sub>y</sub>/GaN structure used earlier. Both samples were annealed in nitrogen at 800°C for 1 h after the SiO2 deposition. When the thickness of the SiO2 dielectric was increased to 90 nm, the negative effects brought by the GaO<sub>x</sub>N<sub>y</sub> interlayer could be suppressed, resulting in little difference in the breakdown and leakage characteristics between the samples with or without the interlayer.

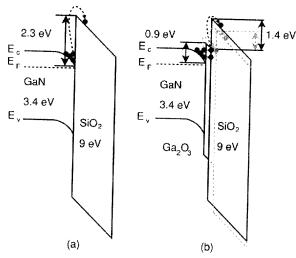

Figure 6 depicts the energy-band diagram for a GaN MIS capacitor with a positive gate bias, and the interlayer is simplified as  $Ga_2O_3$  with a smaller conduction-band offset ( $\Delta E_c = 0.9$  eV) than  $SiO_2$  ( $\Delta E_c = 2.3$  eV). For very thin interlayer, electrons can directly tunnel through it to the  $Ga_2O_3/SiO_2$  interface. For thicker interlayer, the Fowler-Nordheim (FN) tunneling and thermionic emission dominate, and make the electrons jump to the conduction band of the  $Ga_2O_3$  interlayer. Under the same electric field in the  $SiO_2$  layer, the electrons at the  $GaN/SiO_2$  interface have the highest barrier of 2.3 eV to overcome (Fig. 6a): the electrons after direct

Figure 6. (Color online) Energy-band diagram of gate dielectric on GaN. (a) SiO<sub>2</sub>/GaN, (b) SiO<sub>2</sub>/Ga<sub>2</sub>O<sub>3</sub>/GaN. Black balls represent the electrons when Ga<sub>2</sub>O<sub>3</sub> is thin to have direct tunneling dominant; gray balls represent the electrons when Ga2O3 is thicker to have FN tunneling and thermionic emission dominant.

tunneling through the Ga<sub>2</sub>O<sub>3</sub> interlayer see a lower barrier of 1.4 eV (solid arrow in Fig. 6b); and the electrons after FN tunneling through the Ga2O3 interlayer face the lowest barrier of less than 1.4 eV (dotted arrow in Fig. 6b). Thus, we can deduce that the thinner the interlayer, the lower the leakage current because the existence of the interlayer lowers the barrier. For the NS-N2 sample, it should have the thinnest interlayer, which makes the dielectric conduction mechanism mainly decided by the SiO2 layer. The NS-NO sample has Ga ions outdiffused into the SiO2 layer to produce a thicker interlayer (see Fig. 1), and the resulting lower barrier leads to an increase of leakage current. If the SiO2 thickness increases, the SiO2 layer dominates the conduction mechanism, and thus the electrons will find it harder to go through the SiO2 layer by the thermionic emission or FN tunneling. Therefore, we can conclude that by decreasing the interlayer thickness or increasing the SiO<sub>2</sub> thickness, the leakage current can be effectively reduced, which can be well supported by our experimental results.

Therefore, it is expected that through optimizing the thicknesses of SiO2 and GaO3N,, low oxide-charge density, good interface quality, and high breakdown field could be simultaneously achieved.

## Conclusions

NO annealing was applied on both SiO2/GaN and SiO<sub>2</sub>/GaO<sub>3</sub>N<sub>3</sub>/GaN MIS structures and turned out to effectively reduce fixed oxide charges by about one order. Nitrogen and oxygen atoms (decomposed from NO) forming bonds with the dangling Si or Ga in the gate dielectric was the main reason for the reduction of positive oxide charges. The NO annealing was also shown to suppress the border traps for the same reason. A very thin GaO<sub>x</sub>N<sub>y</sub> interlayer formed by thermal oxidation can improve the interface quality and achieve a low interface-trap density  $D_{\rm it}$  of 5.9

$\times~10^{10}~\rm{cm^{-2}}.$  After the NO annealing,  $D_{\rm it}$  of the SiO<sub>2</sub>/GaN capacitor was reduced by about half due to the formation of a  $GaO_\tau N_\nu$ interlayer by the chemical reaction between GaN and NO. The  $D_{it}$  of the SiO<sub>2</sub>/GaO<sub>x</sub>N<sub>y</sub>/GaN structure increased after the NO annealing, implying that too many nitrogen and oxygen atoms (decomposed from NO) piling up at the interface could also have deteriorated the interface quality. According to the breakdown field  $E_{

m BD}$  and leakage current characteristics, SiO<sub>2</sub>/GaN capacitor annealed in nitrogen achieved the highest  $E_{\mathrm{BD}}$  and lowest leakage current. After the NO annealing,  $E_{\mathrm{BD}}$  was degraded for the sample without the  $\mathrm{GaO_{x}N_{y}}$ interlayer, but improved for the sample with the interlayer. SIMS results reveal that the opposite phenomenon should be due to the formation of SiGaON glass throughout the SiO2 dielectric in the former, and the blocking of Ga out-diffusion by the interlayer in the latter. After increasing the SiO2 thickness to 90 nm, the differences in  $E_{\mathrm{BD}}$  and leakage characteristics between the stacked and nonstacked samples were negligible. Therefore, it should be possible that interface quality, oxide charges, and  $E_{\rm BD}$  could be all improved through optimizing the SiO2 thickness and NO-annealing condi-

# Acknowledgment

This work is supported by the RGC of HKSAR, China (project no. HKU 7163/03E). The authors wish to acknowledge K.M. Lau for providing the GaN wafers.

University of Hong Kong assisted in meeting the publication costs of this article.

### References

- H. Morkoç, Nitride Semiconductors and Devices, p. 1, Springer, Berlin (1999).

V. Hoël, Y. Guhel, B. Boudart, C. Gaquière, J. C. De Jaeger, H. Lahrèche, and P. Gibart, Electron. Lett., 37, 1095 (2001).

A. Chini, J. Wittich, S. Heikman, S. Keller, S. P. DenBaars, and U. K. Mishra, IEEE Electron Device Lett., 25, 55 (2004).

- A. P. Edwards, J. A. Mittereder, S. C. Binari, D. S. Katzer, D. F. Storm, and J. A. Roussos, *IEEE Electron Device Lett.*, 26, 225 (2005).

- T. Hashizume, S. Ootomo, T. Inagaki, and H. Hasegawa, J. Vac. Sci. Technol. B, 21. 1828 (2003)

- K. Matocha, T. P. Chow, and R. J. Gutmann, IEEE Trans. Electron Devices, 52, 6

- H. Kim, S. J. Park, and H. Hwang, *J. Vac. Sci. Technol. B*, **19**, 579 (2001).

F. Ren, M. Hong, S. N. G. Chu, M. A. Marcus, M. J. Schurman, A. Baca, S. J. Pearton, and C. R. Abernathy. *Appl. Phys. Lett.*, **73**, 3893 (1998).

J. Kim, R. Mehandru, B. Luo, F. Ren, B. P. Gila, A. H. Onstine, C. R. Abernathy.

- S. J. Pearton, and Y. Irokawa, Appl. Phys. Lett., 81, 373 (2002).

S. Arulkumaran, T. Egawa, H. Ishikawa, T. Jimbo, and M. Umeno, Appl. Phys.

- Lett., 73, 809 (1998).

- J. Kim, R. Mehandru, B. Luo, F. Ren, B. P. Gila, A. H. Onstine, C. R. Abernathy,

- S. J. Pearton, and Y. Irowaw, Appl. Phys. Lett., 80, 4555 (2002). Y. Nakano, T. Kahi, and T. Jimbo, Appl. Phys. Lett., 83, 4336 (2003). K. Matocha, R. J. Gutmann, and T. P. Chow, IEEE Trans. Electron Devices, 50, 1200 (2003).

- L. L. Smith, S. W. King, R. J. Nemanich, and R. F. Davis, J. Electron. Mater., 25,

- M. Gezzo and D. M. Brown, J. Electrochem. Soc., 120, 146 (1973).

A. H. V. Ommen, J. Appl. Phys., 57, 1872 (1985).

C. J. Pan, G. C. Chi, B. J. Pong, J. K. Sheu, and J. Y. Chen, J. Vac. Sci. Technol. B.

- H. C. Casey, G. G. Foutain, R. G. Alley, B. P. Keller, and S. P. DenBaars, *Appl. Phys. Lett.*. **68**, 1850 (1996).

- N. Bhat and K. C. Saraswat, J. Appl. Phys., 84, 2722 (1998).

- D. K. Schroder, Semiconductor Material and Device Characterization, 2nd ed., p. 377, John Wiley & Sons, New York (1998).

- 21. E. H. Nicollian and J. R. Brews, MOS (Metal Oxide Semiconductor) Physics and

- Technology, p. 96. John Wiley & Sons, New York (2003).

22. H. W. Jang, J. K. Kim, C. M. Jeon, and J. L. Lee, MRS Internet J. Nitride Semicond. Res., 6, 8 (2001).