# A Study on Theoretical Representation of Intermodulation in CMOS Balanced Mixers

Jun Wang and Alfred K.K. Wong

Department of Electronic and Electrical Engineering University of Hong Kong, Pokfulam Road, Hong Kong

E-mail: junwang@eee.hku.hk

Abstract—Intermodulation of CMOS balanced mixers is analyzed in this paper with the aim to reduce the effects of intermodulation distortion into a set of simple equations. The analysis consists of a theoretical study and simulation results. Analysis and simulations results reveal that the mechanism of intermodulation in balanced mixer is too complex to be represented by simple equations. Numerical methods must be used to predict the effects of intermodulation in balanced mixer.

#### I. INTRODUCTION

With the increasing demand for highly integrated transceivers, the bulk off-chip filters used in the conventional doubleconversion (heterodyne) receivers have been an obstacle to the increase level of integration. Several transceiver architectures were proposed in the last decade [1-4]. Among them, the Direct Conversion Receiver [1] is promising because the radio-frequency (RF) signals are transfer to baseband directly. In this architecture, the bulk off-chip intermediate-frequency (IF) filters and image rejection filters can be eliminated. However, direct conversion receiver exhibits some disadvantage comparing to conventional heterodyne receivers [1][2]. One critical problem of direct conversion receivers is mismatch-induced second-order intermodulation which decreases the dynamic range of

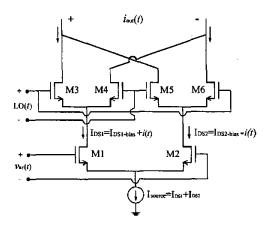

As critical blocks in the front-end of wireless transceivers, mixers are very susceptible to mismatch effects. The double-balanced CMOS mixer [5][6], as shown in Fig.1, is a commonly used topology in CMOS integrated receivers for frequency translation. Intermodulation distortions of double-balanced CMOS mixers have been analyzed extensively in literature [7–9]. However, these analyses usually concentrate only on the third-order intermodulation. Although the numerical method in [5] can be used to calculate the second-order intermodulation, it does not offer intuition on the effects of mismatch in the performance of mixer. An attempt was made in [10], but the resulting model cannot well-predict the second-order intermodulation in high frequency operation.

This paper performs a theoretical analysis of second-order intermodulation caused by mismatches in CMOS double-balanced mixer. A description of intermodulation in receivers will be presented in Section II. The theoretical analyses of single- and double-balanced mixers are discussed in Section III. Section IV details the simulation results and section V summarizes the work.

Fig.1 Double-balanced CMOS mixer [10].

Fig.2 Definition of input dynamic range.

# II. EFFECT OF INTERMODULATIONS ON DYNAMIC RANGE

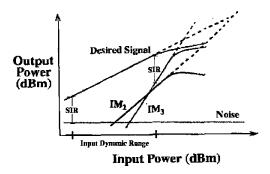

One important characteristics of a receiver is the range of input signals over which the receiver can recognize data correctly (Dynamic Range). This is determined by the signal-to-interference ratio (SIR) required by the back-end of the receiver to reconstruct data from the frond-end of receiver output.

Typically, there are two kinds of interference. One is noise. It determines the low-end of the input range because noise is generally low-amplitude and its magnitude does not vary with the amplitude of input signals. When the input signals become large, intermodulation caused by nonlinearity of the circuits becomes

more important and this determines the high-end of the input range, as shown in Fig.2.

Generally, the transfer function of a circuit may be expressed by a Taylor series expansion:

$$Out(t) = a \cdot In(t) + b \cdot [In(t)]^2 + c \cdot [In(t)]^3 + \cdots$$

(1)

The terms  $b \cdot [In(t)]^2$  and  $c \cdot [In(t)]^3$  represent the second- and third-order response respectively. They generate undesirable spectral components in the output signals. For a typical Superheterodyne receiver, only the third-order intermodulation is close to the channel of interest. But both second- and third-order terms interfere with the desired signal in a Direct-conversion receiver because all these signals are located in baseband. So the largest input signal of a Direct-conversion receiver can be calculate by solving this equation:

$$\frac{a \cdot In}{b \cdot In^2 + c \cdot In^3} = SIR . \tag{2}$$

One way to reduce the effect of second-order intermodulation is the use of a differential structure in the circuit, such as the switch pair in balanced mixers. If there is perfect matching between the two switch transistors (e.g., transistors M3 and M4 in Fig.1), parameter b should be zero. In an actual circuit, mismatch between the two switch transistors will destroy the symmetry of the balanced mixer, so b can be reduced but not eliminated. Even so, when mismatch is not very large,  $b \cdot [In(t)]^2$  is still much smaller than  $c \cdot [In(t)]^3$  near the high-end of the input range, as shown in Fig.2. In this scenario, Equ.2 can be simplified to:

$$\frac{a \cdot In}{c \cdot In^3} = SIR \qquad \Rightarrow \qquad In_{\text{max}} = \sqrt{\frac{a}{c \cdot SIR}} \ . \tag{3}$$

With the decrease of transistor dimension, mismatch will become more and more severe. When the second-order intermodulation become comparable to the third-order intermodulation near the maximum of the input dynamic range (typically about -10~-20dBm), their effect cannot be ignored anymore. The figures of merit are also specified by IIP2 and IIP3, For example, IIP2 represents the fictitious input amplitude at which the energy of the second-order intermodulation output becomes equal to the desire output.

## III. INTERMODULATION ANALYSIS IN BALANCED MIXER

## A. Single-balanced mixer.

Typical operating frequency of wireless receivers ranges from several hundred mega Hz to several giga Hz. In such a high frequency, the effects of capacitors inside the mixer must be considered. These capacitors include the gate-source and source-body capacitors of the switch transistors and the drain-body capacitance of the RF input transistor.

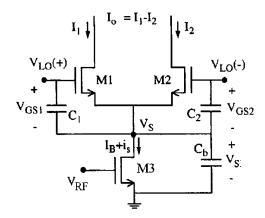

Fig.3 is schematic of single-balanced mixer.  $V_{\rm LO}$  is the local oscillator signal.  $I_{\rm B}$  is the bias current of RF input transistor.  $i_{\rm s}$  is the small current signal converted from the input RF signal.  $C_1$  and  $C_2$  are the gate-source capacitors of the transistors M1 and M2 respectively. The total capacitance from the common-source node to ground consisting of the source—body capacitance of M1 and M2 and the drain—body capacitance of RF input transistor is represented by  $C_{\rm b}$ .

Denoting the I-V relation of a transistor by I = f(V), the behavior of the switching pair can be described by the following [8]:

Fig. 3 Schematic of single-balanced mixer [8].

$$I_{B} + i_{s} = f_{1}(V_{1}) + f_{2}(V_{2}) - C_{b} \frac{d(V_{S})}{dt} \dots + C_{1} \frac{d(V_{GS1} - V_{S})}{dt} + C_{2} \frac{d(V_{GS2} - V_{S})}{dt}.$$

(4)

Because  $V_{LO} = V_{GS1} - V_{GS2}$  , we can re-write Equ.1 as:

$$\begin{split} I_B + i_s &= f_1(V_{GS1}) + f_2(V_{GS2}) \dots \\ &+ \frac{1}{2} (C_1 - C_2) \frac{d(V_{LO})}{dt} - (C_b + C_1 + C_2) \frac{d(V_S)}{dt}, \end{split}$$

Setting  $V_{LO} = A_{LO} \cos(\varpi_{LO}t)$ ,  $\Delta C = \frac{1}{2}(C_1 - C_2)$  and  $C = (C_h + C_1 + C_2)$ , Equ.2 can be simplified as:

$$I_B + \underbrace{\left[i_S + \Delta C \varpi_{LO} A_{LO} \sin(2\pi f_{LO} t)\right]}_{\text{Equivalent small input current signals}} = -C \frac{d(V_S)}{dt} \dots$$

(6)

+

$$f_1(V_{GS1})h + f_2(V_{GS2})$$

Typically  $\Delta C \varpi_{LO} A_{LO}$  is small compared with the bias current. So it can be treated as a small input signal of the switch pair with the same frequency of LO.

From Equ.6, it can be concluded that the LO signal will leak into the input of the switch pair due to capacitor mismatch of the two switch transistors. The leakage becomes more severe with increase of the frequency or the amplitude of LO.

Using the result in [8], the output current of the switch pair can be represented using the time-varying Volterra series [11-13], such that:

$$\begin{split} I_{out} &= f_1(V_{GS1}) - f_2(V_{GS2}) \\ &= I_{out-DC} + i_{out}(t) \\ &= P_0(t) \cdot I_B + P_1(t, f_a) \circ i + P_2(t, f_a, f_b) \circ i^2 \dots \\ &\quad + P_3(t, f_a, f_b, f_c) \circ i^3 + \dots \end{split}$$

(7)

where  $I_B$  and i are the bias and small signal input current of the switch pair respectively, and  $P_i$ , i=1,2,3... are the Volterra series coefficients. They can be calculated by the numerical method described in [8]. If there is a perfect match between the two transistors in the switch pair, all the even-order Fourier coefficients of  $P_i$  will be zero. In an actual circuit, they are always nonzero due to mismatch.

Because the RF input transistor M3 in Fig.3 is a timeinvariant nonlinear circuit, it can be represented using the traditional Tyler-series. Assume  $v_{rf} = r_{rf} \cos(\varpi_{rf} t)$  is the input RF small signal, the input current of the switch pair can be written as:

$$\begin{split} I_{input} &= I_B + i_{RF} + i_{LO\_leakage} \\ &= I_B + a \cdot v_{rf} + b \cdot v_{rf}^2 + c \cdot v_{rf}^3 \dots \\ &+ \Delta C A_{LO} \boldsymbol{\varpi}_{LO} \sin(\boldsymbol{\varpi}_{LO} t) \end{split} \tag{8}$$

Substituting Equ.7 into Equ.8, using  $p_{i,j}$  as the j-th order Fourier coefficient of  $P_i$  and a, b and c are first-, second- and third-order transfer characteristics of RF input transistor, and through some mathematical manipulation and simplification, we obtain equations for the first 4 orders of the output current as below:

order output (DC-feedthrough):

$$I_{out-DC} = p_{0,0} \cdot I_B + p_{1,1} \cdot \frac{\Delta C A_{LO} \overline{\omega}_{LO}}{2}, \tag{9}$$

• 1st-order output (Desired):

$$i_{desire} \approx (p_{1,1} \cdot a) \cdot r_{rf} , \qquad (10)$$

• 2nd-order output (IM2):

$$i_{lM2} = \left(p_{2,0} \cdot a^2 + p_{3,1} \cdot \frac{\Delta CA_{LO} \sigma_{LO}}{2} \cdot a^2 + p_{0,0} \cdot \frac{b}{2}\right) \cdot r_{rf}^2,$$

(11)

3rd-order output (IM3):

$$i_{IM3} = \left(p_{3,1} \cdot a^3 + p_{1,1} \frac{3}{4}c\right) \cdot r_{rf}^3. \tag{12}$$

From Equ.9 and Equ.11, it can be found that the DC-feedthrough and IM2 will increase with increasing frequency, while the desired output signal is virtually unchanged with frequency. That means the DC-feedthrough and the IP2 will decrease with increasing frequency.

## B. Doubled-balanced mixer.

After obtaining the equations for the output of single-balanced mixers, it is not difficult to get the equations for double-balanced mixers from the result of single-balanced mixer by inputting two single-balanced mixers with RF signal in opposite phase and subtracting one output from the other:

• 0-order output (DC-feedthrough):

$$I_{out-DC} = \Delta p_{0,0} \cdot I_B + p_{1,1} \cdot \frac{\Delta \Delta C A_{LO} \overline{\sigma}_{LO}}{2}, \qquad (13)$$

1st-order output (Desired):

$$i_{desire} \approx (p_{1,1} \cdot a) \cdot r_{rf}$$

, (14)

• 2nd-order output (IM2):

$$i_{IM2} = \left(\Delta p_{2,0} \cdot a^2 + p_{3,1} \cdot \frac{\Delta \Delta C A_{LO} \varpi_{LO}}{2} \cdot a^2 + \Delta p_{0,0} \cdot \frac{b}{2}\right) \cdot \frac{r_{rf}^2}{4}$$

(15)

• 3rd-order output (IM3):

$$i_{IM3} = \left(p_{3,1} \cdot a^3 + p_{1,1} \frac{3}{4}c\right) \cdot \frac{r_{rf}^3}{4}.$$

(16)

One assumption is used in the course to get these equations. That is: when j is an even, no matter  $p_{i,j}$  or  $\Delta p_{i,j}$ ,  $\Delta C$  or  $\Delta \Delta C$ , they are all random numbers with mean of zero and small variances comparing with a or b.

Two conclusions can be reached from Equ.13 to Equ.16 for the double-balanced mixer. First, only the mismatch in the switch pair is important for the output DC-feedthrough and IIP2, the mismatch in the input RF converter almost has no any effects for DC-feedthrough and IIP2. The second, the variances of  $\Delta p_{i,i}$

and  $\Delta\Delta C$  are  $\sqrt{2}$  times of those of  $p_{i,j}$  and  $\Delta C$  respectively. The DC-feedthrough of double-balanced mixer will increase 3 dBm compare with that of single-balanced mixer while IIP2 will also increase 9 dBm statistically.

#### IV. SIMULATION RESULTS

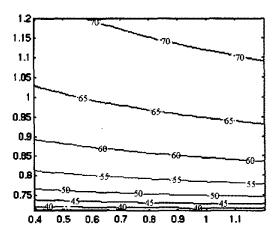

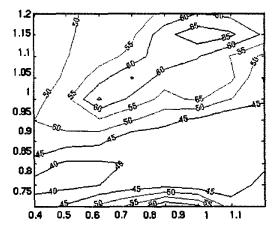

Because the value of parameters  $p_{i,j}$  only can be calculated by numerical methods [8], it is still impossible to use theoretical equations to predict intermodulation of mixer accurately. Instead, we can obtain some qualitative results with the simplification methods found in [10] and [14]. To test the accuracy of the simplified theoretical method, simulations are performed in Matlab and Cadence SpectreRF to calculate the IIP2 of a double-balanced mixer with different transistor width in the input V-I converter and switch pair, as shown in Fig.4 and Fig.5 separately. Amplitude of LO and bias common mode input voltage are the X-axis and Y-axis respectively. The ratio of transistor width

$$\frac{W_{switch}}{W_{CM-input}}$$

is  $\frac{300 \, \mu m}{300 \, \mu m}$  . The model in Section III is simplified by

the methods in [10] and [14] so that it can be represented by a set of equations and calculated in Matlab. Fig.4 is the result of Matlab.

Fig.4 Calculation results of IIP2 using Matlab.

Fig.5 Simulation results of IIP2 using Cadence SpectreRF.

IIP2 increases with the increasing of the common mode RF input voltage *OR* the amplitude of LO. Figures 5 are the simulation results of SpectreRF. Different from the results of Matlab, in this figure IIP2 increases when the common mode RF input voltage *AND* the amplitude of LO increase. Apparently, theoretical equations are too simplistic to predict IIP2 correctly.

### V. CONCLUSIONS

A study of theoretical representation of intermodulation of CMOS balanced mixer has been performed. Time- variance and nonlinearity characteristics of switch pair in balanced mixer make it too complex to be described by simply equations. Although qualitative results can be obtained by the described theoretical method, accurate quantification of intermodulation can only be predicted by numerical methods.

### REFERENCES

- A. A. Abidi, "Direct-conversion radio transceivers for digital communications," *IEEE J. Solid-State Circuits*, vol. 30, pp. 1399-1410, Dec. 1995.

- B. Razavi, "Design considerations for direct conversion receiver," *IEEE Trans. Circuits Syst. II*, vol. 44, pp. 428-435, June 1997.

- J. Crols and M. S. J. Steyaert, "A single-chip 900 MHz CMOS receiver front-end with a high performance low-IF topology," *IEEE J. Solid-State Circuits*, vol. 30, no. 12, Dec. 1995

- J. Crols and M. S. J. Steyaert, "Low-IF topology for highperformance analog front-end of full integrated receivers," IEEE Trans. on Circuits and System II: Analog and Digital Signal Processing, vol. 45, no. 3, Mar. 1998.

- B. Gilbert, "A precise four quadrant multiplier with sub nanosecond response," *IEEE J. Solid-State Circuits*, vol. SC-3, pp.365-373, Dec. 1968.

- T. H. Lee, The design of CMOD radio-frequency integrated circuits, pp. 319-322, Cambridge University, 1998.

- R. C. Meyer, "Intermodulation in high-frequency bipolar transistor integrated circuit mixers," *IEEE J. Solid-State Circuits*, vol. SC-21, pp. 534-537, Aug. 1986.

- M. T. Terrovitis and R. G. Meyer, "Intermodulation distortion in current-commutating CMOS mixers," *IEEE J. Solid-State Circuits*, vol. 35, NO. 10, pp. 1461-1473, Oct. 2000

- K. L. Fong and R. G. meyer, "High-frequency nonlinearity analysis of common-emitter and differential-pair transconductance stages," *IEEE J. Solid-State Circuits*, vol. 33, pp. 548-555, Apr. 1998.

- J. Wang and A. K. K. Wong, "Effects of mismatch on CMOS double-balanced mixers: a theoretical analysis", IEEE Proceedings Hong Kong 2001, Electron Devices Meeting, 2001, pp. 85-88

- R. B. Swerdlow, "Analysis of Intermodulation Noise in Frequency Con-verters by Volterra Series," *IEEE Trans. Microwave Theory and Tech-niques* vol. MTT-26, pp. 305–313, Apr. 1978.

- S. Maas, "Two-tone intermodulation in diode mixers," *IEEE Trans. Mi-crowave Theory and Techniques*, vol. MTT-35, pp. 307–314, Mar. 1987.

- S. Maas and D. Neilson, "Modeling MESFETs for intermodulation analysis of mixers and amplifiers," *IEEE Trans. Microwave theory and Techniques*, vol. 38, pp. 1964–1971, Dec. 1990

H. Darabi and A. A. Abidi, "Noise in RF-CMOS mixers: a simple physical model," *IEEE Trans. on Solid State Circuits*, vol. 35, no. 1, pp. 15-25, Jan. 2000.